## **Product Specification**

# **PE4140**

## Ultra-High Linearity UltraCMOS™ **Broadband Quad MOSFET Array**

#### **Features**

- Ultimate Quad MOSFET array

- Ultra-high linearity, broadband performance beyond 6.0 GHz

- Ideal for mixer applications

- Up/down conversion

- Low conversion loss

- High LO Isolation

- Packaged in small 6-lead 3x3 mm DFN

#### **Product Description**

The PE4140 is an ultra-high linearity passive broadband Quad MOSFET array with high dynamic range performance capable of operation beyond 6.0 GHz. This guad array operates with differential signals at all ports (RF, LO, IF), allowing mixers to be built that use LO powers from -7 dBm to +20 dBm. Typical applications range from frequency up/down-conversion to phase detection for Cellular/PCS Base Stations, Wireless Broadband Communications and STB/Cable modems.

The PE4140 is manufactured on pSemi's UltraCMOS™ process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate, offering the performance of GaAs with the economy and integration of conventional CMOS.

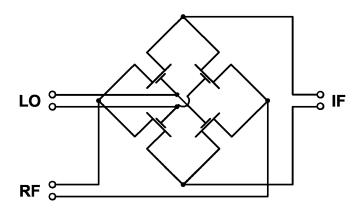

Figure 1. Functional Diagram

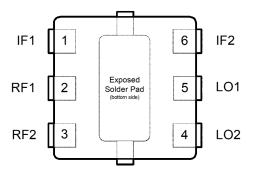

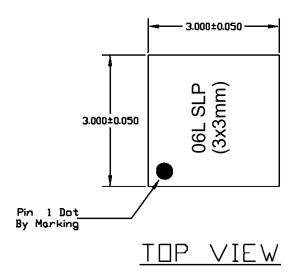

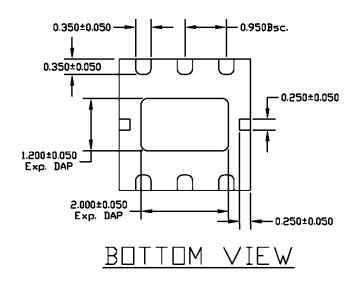

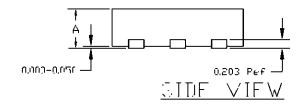

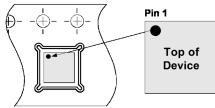

Figure 2. Package Type

6-lead DFN

Table 1. AC and DC Electrical Specifications @ +25 °C

| Symbol                | Characteristics                        | Test Conditions                           | Min | Тур  | Max | Units |

|-----------------------|----------------------------------------|-------------------------------------------|-----|------|-----|-------|

| F <sub>TYP</sub>      | Operating Frequency Range <sup>1</sup> |                                           | DC  |      | 6.0 | GHz   |

| V <sub>DS</sub>       | Drain-Source Voltage                   | $V_{GS} = +3V$ , $I_{DS} = 40 \text{ mA}$ | 260 | 320  | 380 | mV    |

| V <sub>DS</sub> Match | Drain-Source Voltage Match             |                                           |     | 12   | 40  | mV    |

| V <sub>T</sub>        | Threshold Voltage                      | V <sub>DS</sub> = 0.1V; per ASTM F617-00  |     | -100 |     | mV    |

| R <sub>DS</sub>       | Drain-Source 'ON' Resistance           | $V_{GS} = +3V$ , $I_{DS} = 40 \text{ mA}$ | 6.5 | 7.75 | 9.5 | Ω     |

Note 1: Typical untested operating frequency range of Quad MOSFET transistors.

Figure 3. Pin Configuration (Top View)

Table 2. Pin Descriptions

| Pin<br>No. | Pin<br>Name | Description                  |

|------------|-------------|------------------------------|

| 1          | IF1         | IF Output Connection (Drain) |

| 2          | RF1         | RF Input Connection (Source) |

| 3          | RF2         | RF Input Connection (Source) |

| 4          | LO2         | LO Input Connection (Gate)   |

| 5          | LO1         | LO Input Connection (Gate)   |

| 6          | IF2         | IF Output Connection (Drain) |

Table 3. Absolute Maximum Ratings

| Symbol               | rmbol Parameters/<br>Conditions                                                      |     | Max  | Units    |

|----------------------|--------------------------------------------------------------------------------------|-----|------|----------|

| T <sub>ST</sub>      | Storage temperature range                                                            | -65 | 150  | °C       |

| $T_OP$               | Operating temperature range                                                          |     | 85   | ô        |

| V <sub>DC + AC</sub> | Maximum DC plus peak<br>AC voltage across Drain-<br>Source                           |     | ±3.3 | <b>V</b> |

| $V_{DC+AC}$          | V <sub>DC+AC</sub> Maximum DC plus peak AC voltage across Gate- Drain or Gate-Source |     | ±4.2 | V        |

| V <sub>ESD</sub>     | HBM¹ ESD Voltage                                                                     |     | 100  | V        |

Note 1: ML\_STD 883 Method 3015.7

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

This MOSFET device has minimally protected inputs and is highly susceptible to ESD damage. When handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices.

#### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UltraCMOS™ devices are immune to latch-up.

#### **Device Description**

The PE4140 passive broadband Quad MOSFET array is designed for use in up-conversion and down-conversion applications for high performance systems such as cellular infrastructure equipment and STB/CATV systems.

The PE4140 is an ideal mixer core for a wide range of mixer products, including module level solutions that incorporate baluns or other singleended matching structures enabling three-port operation.

The performance level of this passive mixer is made possible by the very high linearity afforded by pSemi's UltraCMOS™ process.

#### Marking

Packaged devices are marked with part number "4140", date code and lot code.

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE4140 in the 6-lead 3x3 DFN package is MSL1.

#### **Evaluation Kit**

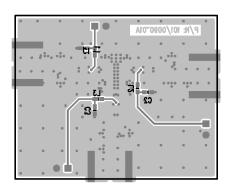

## Figure 4. Evaluation Board Layout

pSemi Specification 101/0090

### **Applications Support**

If you have a problem with your evaluation kit or if you have applications questions, please contact applications support:

E-Mail: help@psemi.com (fastest response)

Phone: (858) 731-9400

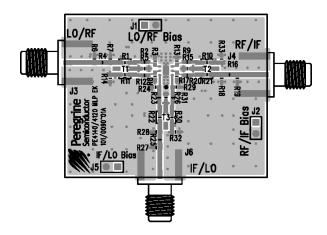

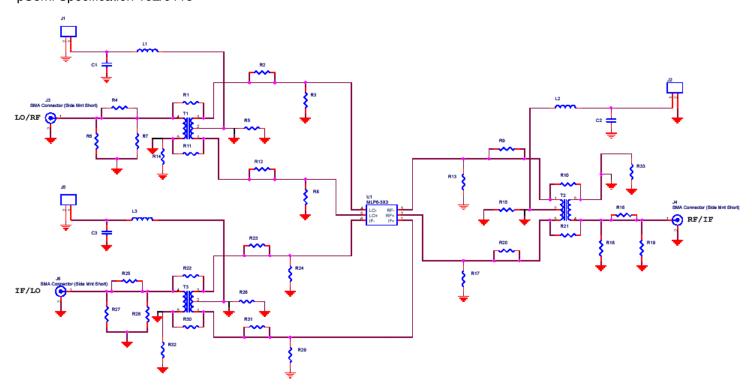

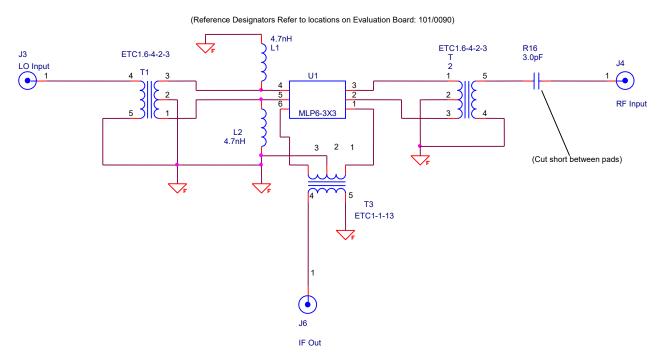

Figure 5. Evaluation Board Schematic

pSemi Specification 102/0115

This is the complete evaluation board schematic; which can be used for multiple configurations. Not all Note: components need be populated. Refer to 'typical schematics' on following pages.

Figure 6. Typical Schematic for a PCS Application

Table 4. Typical Performance in a PCS Application @ +25 °C

| Parameter                | Minimum | Typical | Maximum | Units |  |

|--------------------------|---------|---------|---------|-------|--|

| Frequency Range**        |         |         |         |       |  |

| LO                       | 1630    |         | 2130    | MHz   |  |

| RF                       | 1700    |         | 2200    | MHz   |  |

| IF                       |         | 70      |         | MHz   |  |

| Conversion Loss**        |         | 0.5     |         | AD.   |  |

| (Includes balun losses)  |         | 8.5     |         | dB    |  |

| Isolation**              |         |         |         |       |  |

| LO-RF                    |         | 36      |         | dB    |  |

| LO-IF                    |         | 26      |         | dB    |  |

| Input IP3**              |         | 32      |         | dBm   |  |

| Input 1 dB Compression** |         | 22      |         | dBm   |  |

<sup>\*\*</sup> Data taken on an Evaluation Board narrow-band tuned to cover the PCS band, IF = 73MHz low-side, LO drive = 17dBm.

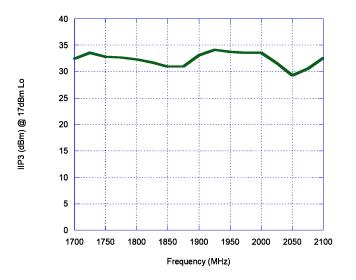

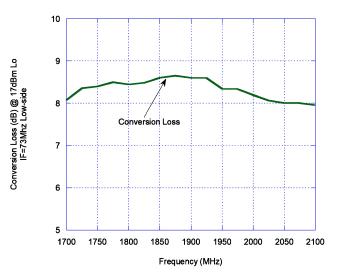

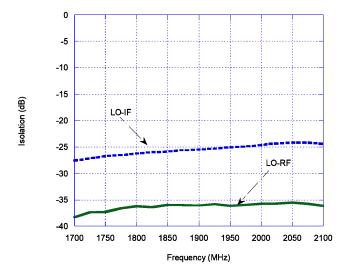

## Typical Performance Plots in a PCS Application @ +25 °C (LO=17 dBm, IF=73 MHz Low-side)

## Figure 7. IIP3 vs. Frequency

Figure 8. Conversion Loss vs. Frequency

Figure 9. LO-RF & LO-IF Isolation

Figure 10. Typical Schematic for a CATV Application

Note: L1 and L2 provide LO port matching for optimum performance. Typical gate capacitance is approximately 2.5 pF.

Table 5. Typical Performance in a CATV Application @ +25 °C

| Parameter                | Minimum | Typical     | Maximum | Units |

|--------------------------|---------|-------------|---------|-------|

| Frequency Range**        |         |             |         |       |

| LO                       | 1116    | <del></del> | 1926    | MHz   |

| RF                       | 54      |             | 864     | MHz   |

| IF                       |         | 1062        |         | MHz   |

| Conversion Loss**        |         | 6.5         |         | dB    |

| (Includes balun losses)  |         | 0.5         |         | uБ    |

| Isolation**              |         |             |         |       |

| LO-RF                    |         | 40          |         | dB    |

| LO-IF                    |         | 28          |         | dB    |

| Input IP3**              |         | 23          |         | dBm   |

| Input 1 dB Compression** |         | 13          |         | dBm   |

<sup>\*\*</sup> Data taken on an Evaluation Board tuned for a broadband CATV application, IF = 1062 MHz, RF drive = -5 dBm, LO drive = 10 dBm.

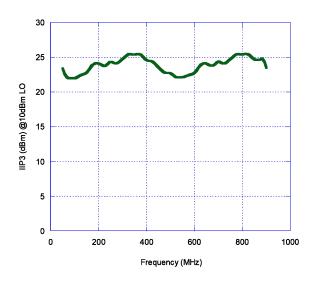

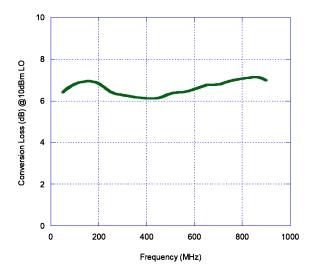

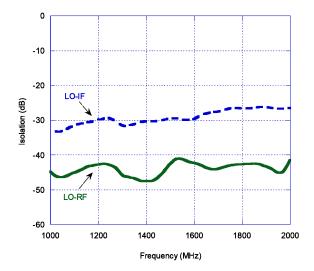

## Typical Performance Plots in a CATV Application @ +25 °C

## Figure 11. IIP3 vs. Frequency

Figure 12. Conversion Loss vs. Frequency

Figure 13. LO-RF & LO-IF Isolation

Figure 14. Package Drawing

6-lead DFN

### NOTE:

IN ISEP AND SEP SHARE THE SAME EXHIBE DUTLINE BUT WITH DIFFERENT THICKNESS:

|    |      | TSLP  | 3LP   |

|----|------|-------|-------|

|    | MAK. | 0.800 | 0.500 |

| ΙA | MUM. | น./5เ | J.とちし |

|    | .АЈМ | 0,700 | າ,ຬດດ |

NOTE: The exposed solder pad (on the bottom of the package) is not electrically connected to any other pin (isolated).

Figure 15. Marking Specifications

Pin 1 indicator

YY = Last two digits of assembly year

WW = Assembly work week

ZZZZZZ = Assembly lot code (maximum six characters)

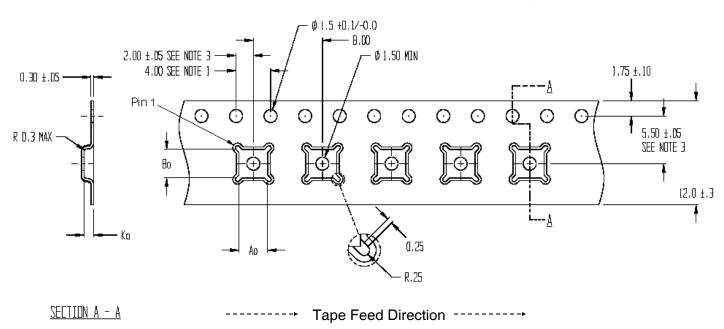

Figure 16. Tape and Reel Specifications

6-lead DFN

Table 6. Dimensions

| Dimension    | DFN 3x3 mm   |

|--------------|--------------|

| Ao           | 3.23 ± 0.1   |

| Во           | 3.17 ± 0.1   |

| Ko           | 1.37 ± 0.1   |

| Р            | 4 ± 0.1      |

| W            | 8 +0.3, -0.1 |

| Т            | 0.254 ± 0.02 |

| R7 Quantity  | 3000         |

| R13 Quantity | N.A.         |

Note: R7 = 7 inch Lock Reel, R13 = 13 inch Lock Reel

Device Orientation in Tape

#### NOTES:

- 1. 10 SPROCKET HOLE PITCH CUMULATIVE TOLERANCE ±0.2

- 2. CAMBER IN COMPLIANCE WITH EIA 481

- 3. POCKET POSITION RELATIVE TO SPROCKET HOLE MEASURED AS TRLE POSITION OF POCKET, NOT POCKET HOLE

#### **Table 7. Ordering Infomation**

| Order Code | Part Marking | Description               | Package                 | Shipping Method  |

|------------|--------------|---------------------------|-------------------------|------------------|

| PE4140B-Z  | 4140         | PE4140G-06DFN 3x3mm-3000C | Green 6-lead 3x3 mm DFN | 3000 units / T&R |

| EK4140-01  | PE4140-EK    | PE4140-06DFN 3x3mm-EK     | Evaluation Kit          | 1 / Box          |

### **Sales Contact and Information**

For additional information, contact Sales at <a href="mailto:sales@psemi.com">sales@psemi.com</a>.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Age-effication: The datasheet contains preliminary data. Additional data may be added at a later date. pSemi reserves the right to change specifications at any time without notice in order to supply the best possible product. Product Specification: The datasheet contains final data. In the event pSemi decides to change the specifications, pSemi will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this document is believed to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this document are implied or granted to any third party.

pSemi's products are not designed or intended to support or sustain life, or for use in any application in

pSemi's products are not designed or intended to support or sustain life, or for use in any application in which the failure of the pSemi product could create a situation in which personal injury or death might occur. pSemi assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.

pSemi products are protected under one or more of the following U.S. patents: patents.psemi.com.