# **Product Description**

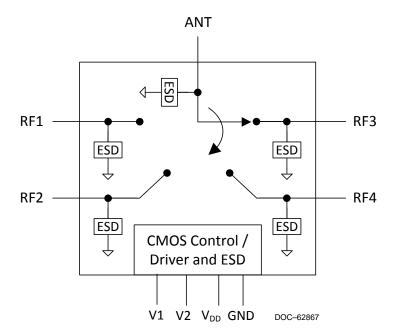

The PE613050 is an SP4T tuning control switch based on Peregrine's UltraCMOS® technology. This highly versatile switch supports a wide variety of tuning circuit topologies with emphasis on impedance matching and aperture tuning applications. PE613050 features low onresistance and insertion loss across key cellular frequency bands from 5 to 3000 MHz.

PE613050 offers high RF power handling and ruggedness, while meeting challenging harmonic and linearity requirements enabled by Peregrine's HaRP™ technology. With two-pin low voltage CMOS control, all decoding and biasing is integrated on-chip and no external bypassing or filtering components are required.

UltraCMOS tuning devices feature ease of use while delivering superior RF performance. With built-in bias voltage generation and ESD protection, tuning control switches provide a monolithically integrated tuning solution for demanding RF applications.

Figure 1. Functional Diagram

# **Product Specification**

# PE613050

UltraCMOS® SP4T Tuning Control Switch, 5–3000 MHz

#### **Features**

- Open reflective architecture

- Low on-resistance of 1.6Ω

- Low insertion loss

- 0.25 dB @ 900 MHz

- 0.40 dB @ 2200 MHz

- High power handling

- 35.1 dBm @ 900 MHz

- 35.1 dBm @ 2200 MHz

- Wide power supply range (2.3V to 5.5V)

- High ESD tolerance of 2 kV HBM on all pins

- Applications include

- Tunable antennas

- Tunable matching networks

- Bypassing applications

- RFID readers

Figure 2. Package Type

12-lead  $2 \times 2 \times 0.5$  mm QFN

Table 1. Electrical Specifications @ 25°C, V<sub>DD</sub> = 2.75V

| Parameter                   | Condition                                                                                | Min | Тур  | Max  | Unit |

|-----------------------------|------------------------------------------------------------------------------------------|-----|------|------|------|

| Operating Frequency         |                                                                                          | 5   |      | 3000 | MHz  |

| R <sub>ON</sub>             | RF-ANT, ON state, DC measurement                                                         |     | 1.6  |      | Ω    |

| C <sub>OFF</sub>            | RF-ANT, any OFF state                                                                    |     | 0.14 |      | pF   |

|                             | RF-ANT 5-100 MHz                                                                         |     | 0.17 |      | dB   |

|                             | RF-ANT 100-698 MHz                                                                       |     | 0.20 | 0.30 | dB   |

|                             | RF-ANT 698-960 MHz                                                                       |     | 0.25 | 0.35 | dB   |

| Insertion Loss <sup>1</sup> | RF-ANT 960-1710 MHz                                                                      |     | 0.35 | 0.45 | dB   |

|                             | RF-ANT 1710-2170 MHz                                                                     |     | 0.40 | 0.50 | dB   |

|                             | RF-ANT 2170-2500 MHz                                                                     |     | 0.45 | 0.55 | dB   |

|                             | RF-ANT 2500-2690 MHz                                                                     |     | 0.50 | 0.60 | dB   |

|                             | RF-ANT 5-100 MHz                                                                         |     | 46   |      | dB   |

|                             | RF-ANT 100-698 MHz                                                                       | 26  | 28   |      | dB   |

|                             | RF-ANT 698-960 MHz                                                                       | 25  | 27   |      | dB   |

| la alatia a <sup>2</sup>    | RF-ANT 960-1710 MHz                                                                      | 21  | 23   |      | dB   |

| Isolation <sup>2</sup>      | RF-ANT 1710-2170 MHz                                                                     | 19  | 21   |      | dB   |

|                             | RF-ANT 2170-2500 MHz                                                                     | 18  | 20   |      | dB   |

|                             | RF-ANT 2500-2690 MHz                                                                     | 17  | 19   |      | dB   |

|                             | RF-ANT 2690-3000 MHz                                                                     | 15  | 17   |      | dB   |

|                             | RF-ANT (2fo: 5 to 100 MHz; +26 dBm @ TX)                                                 |     | -58  |      | dBm  |

|                             | RF-ANT (3fo: 5 to 100 MHz; +26 dBm @ TX)                                                 |     | -87  |      | dBm  |

|                             | RF-ANT (2fo: 698 to 915 MHz; +35 dBm @ TX)                                               |     | -62  | -36  | dBm  |

|                             | RF-ANT (3fo: 698 to 915 MHz; +35 dBm @ TX)                                               |     | -55  | -36  | dBm  |

| Harmonics <sup>3</sup>      | RF-ANT (2fo: 1710 to 1910 MHz; +33 dBm @ TX)                                             |     | -58  | -36  | dBm  |

| Harmonics                   | RF-ANT (3fo: 1710 to 1910 MHz; +33 dBm @ TX)                                             |     | -55  | -36  | dBm  |

|                             | RF-ANT (2fo: 698 to 798 MHz; +26 dBm @ TX)                                               |     | -80  | -36  | dBm  |

|                             | RF-ANT (3fo: 698 to 798 MHz; +26 dBm @ TX)                                               |     | -82  | -36  | dBm  |

|                             | RF-ANT (2fo: 2500 to 2570 MHz; +26 dBm @ TX)                                             |     | -70  | -36  | dBm  |

|                             | RF-ANT (3fo: 2500 to 2570 MHz; +26 dBm @ TX)                                             |     | -70  | -36  | dBm  |

| Input IP3                   | 5–100 MHz                                                                                |     | 80   |      | dBm  |

|                             | 100–3000 MHz                                                                             |     | 72   |      | dBm  |

| IMD3                        | Bands I,II,V,VIII, +20 dBm CW @ TX freq, -15 dBm CW @ 2TX-RX freq, 50Ω, SW <sub>ON</sub> |     | -120 | -105 | dBm  |

| Switching Time              | 50% VCTRL to 90% RF ON or 10% RF OFF                                                     |     | 2    | 5    | μs   |

| Start-up Time <sup>3</sup>  | Time from V <sub>DD</sub> within specification to all performances within specification  |     |      | 70   | μs   |

Notes: 1. Tapered transmission lines on evaluation board provide optimal matching; no additional components on evaluation board required to meet specified performance. See Figure 5 for evaluation board layout.

<sup>2.</sup> Open reflective architecture for flexible configuration of switch in tuning application.

3. Pulsed RF input with 4620 µs period, 50% duty cycle, measured per 3GPP TS 45.005.

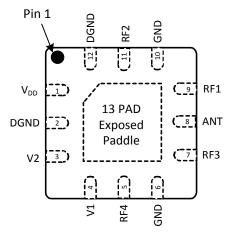

Figure 3. Pin Configuration (Top View)

Table 2. Pin Descriptions

| Pin No. | Pin Name | Description                            |

|---------|----------|----------------------------------------|

| 1       | $V_{DD}$ | Supply                                 |

| 2       | DGND     | Digital Ground                         |

| 3       | V2       | Switch control input, CMOS logic level |

| 4       | V1       | Switch control input, CMOS logic level |

| 5       | RF4      | RF I/O                                 |

| 6       | GND      | Ground <sup>1</sup>                    |

| 7       | RF3      | RF I/O                                 |

| 8       | ANT      | RF Common - Antenna                    |

| 9       | RF1      | RF I/O                                 |

| 10      | GND      | Ground <sup>1</sup>                    |

| 11      | RF2      | RF I/O                                 |

| 12      | DGND     | Digital Ground <sup>1</sup>            |

| 13      | PAD      | Exposed Paddle <sup>2</sup>            |

Notes: 1. All ground pins must be tied together (pins 6, 10, 12).

Recommend grounding but can be left floating.

## **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE613050 in the 12-lead 2  $\times$  2 mm QFN package is MSL1.

**Table 3. Truth Table**

| Path    | V2 | V1 |

|---------|----|----|

| RF1-ANT | 0  | 0  |

| RF2-ANT | 1  | 0  |

| RF3-ANT | 0  | 1  |

| RF4-ANT | 1  | 1  |

**Table 4. Operating Ranges**

| Parameter                                                                             | Min  | Тур  | Max                                                   | Unit                                                  |

|---------------------------------------------------------------------------------------|------|------|-------------------------------------------------------|-------------------------------------------------------|

| V <sub>DD</sub> Supply Voltage                                                        | 2.30 | 2.75 | 5.50                                                  | V                                                     |

| I <sub>DD</sub> Power Supply Current<br>(V <sub>DD</sub> = 2.75V, +25 °C)             |      | 140  | 200                                                   | μΑ                                                    |

| V <sub>IH</sub> Control Voltage High                                                  | 1.2  | 1.5  | 3.1                                                   | V                                                     |

| V <sub>IL</sub> Control Voltage Low                                                   | 0    | 0    | 0.5                                                   | ٧                                                     |

| Control Input Current                                                                 |      | 1    | 10                                                    | μΑ                                                    |

| Peak Operating RF Voltage <sup>1,2</sup><br>5–100 MHz<br>100 MHz–1 GHz<br>1 GHz–3 GHz |      |      | 10 <sup>5</sup><br>18 <sup>3</sup><br>18 <sup>4</sup> | V <sub>PK</sub><br>V <sub>PK</sub><br>V <sub>PK</sub> |

| T <sub>OP</sub> Operating Temperature Range                                           | -40  | +25  | +85                                                   | °C                                                    |

otes: 1. Between all RF ports, and from RF ports to GND.

- 2. Pulsed RF input duty cycle of 50% and 4620  $\mu$ s, measured per 3GPP

- TS 45.005.

- 3. RF input power of 35.1 dBm,  $50\Omega$ .

- 4. RF input power of 35.1 dBm,  $50\Omega$ .

- 5. RF input power of 30.0 dBm,  $50\Omega$ .

**Table 5. Absolute Maximum Ratings**

| Symbol               | Parameter/Conditions           | Min  | Max  | Unit |

|----------------------|--------------------------------|------|------|------|

| $V_{DD}$             | Supply Voltage                 | -0.3 | 5.5  | V    |

| V <sub>CTRL</sub>    | Digital Input Voltage (V1, V2) | -0.3 | 3.6  | V    |

| T <sub>ST</sub>      | Storage Temperature Range      | -65  | +150 | °C   |

| V <sub>ESD,HBM</sub> | HBM ESD Voltage, All Pins*     |      | 2000 | V    |

Note: \* Human Body Model (MIL\_STD 883 Method 3015.7).

Exceeding absolute maximum ratings may cause permanent damage. Operating should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating.

#### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UltraCMOS devices are immune to latch-up.

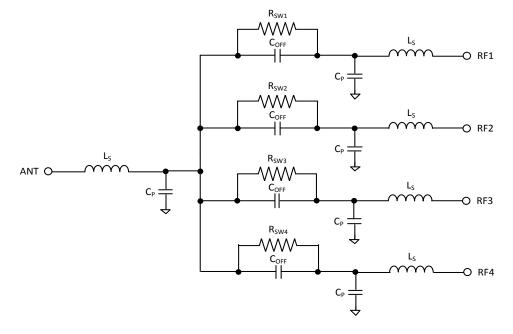

## **Equivalent Circuit Model Description**

The Equivalent Circuit Model shown in *Figure 4* can be used to accurately model the impedance, insertion loss, and isolation of the SP4T Tuning Switch. It provides a very close correlation to measured data and can easily be used in circuit simulation programs.

Table 7 provides the mapping between the desired switch RF state (RF1 thru RF4) and the state variables (SW1 thru SW4).

The equivalent circuit model parameter values can be calculated using equations shown in *Table 6*.

**Table 6. Equivalent Circuit Model Parameters**

| Variable         | Equation (SW=0 for OFF and SW=1 for ON)    | Unit |

|------------------|--------------------------------------------|------|

| C <sub>P</sub>   | 0.25                                       | pF   |

| $C_{OFF}$        | 0.14                                       | pF   |

| R <sub>SW1</sub> | If $SW_1 == 1$ then 1.6 else 400e3         | Ω    |

| R <sub>SW2</sub> | If SW <sub>2</sub> == 1then 1.6 else 400e3 | Ω    |

| R <sub>SW3</sub> | If SW <sub>3</sub> == 1then 1.6 else 400e3 | Ω    |

| R <sub>SW4</sub> | If SW <sub>4</sub> == 1then 1.6 else 400e3 | Ω    |

| Ls               | 0.4                                        | nH   |

**Table 7. Equivalent Circuit Model Variables**

| RF State |    |    | Variable |     |     |     |

|----------|----|----|----------|-----|-----|-----|

| Path     | V2 | V1 | SW1      | SW2 | SW3 | SW4 |

| RF1-ANT  | 0  | 0  | 1        | 0   | 0   | 0   |

| RF2-ANT  | 1  | 0  | 0        | 1   | 0   | 0   |

| RF3-ANT  | 0  | 1  | 0        | 0   | 1   | 0   |

| RF4-ANT  | 1  | 1  | 0        | 0   | 0   | 1   |

Figure 4. Equivalent Circuit Model Schematic

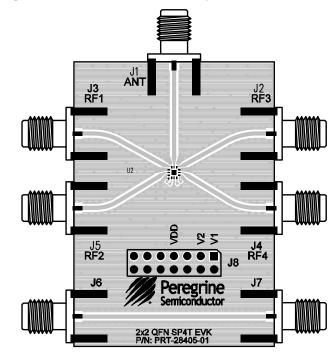

#### **Evaluation Board**

The SP4T switch Evaluation Board was designed to ease customer evaluation of Peregrine's PE613050. The RF common port is connected through a 50Ω transmission line via the top SMA connector, J1. RF1, RF2, RF3 and RF4 are connected through 50Ω transmission lines via SMA connectors J3, J5, J2 and J4, respectively. A through 50Ω transmission is available via SMA connectors J6 and J7. This transmission line can be used to estimate the loss of the PCB over the environmental conditions being evaluated.

The board consists of a 4 layer stack with 2 outer layers made of Rogers 4350B ( $\varepsilon_r = 3.48$ ) and 2 inner layers of FR4 ( $\varepsilon_r = 4.80$ ). The total thickness of this board is 62 mils (1.57 mm). The inner layers provide a ground plane for the transmission lines. Each transmission line is designed using a coplanar waveguide with ground plane (CPWG) model using a trace width of 32 mils (0.813 mm), gap of 15 mils (0.381 mm), and a metal thickness of 1.4 mils (0.051 mm).

Figure 5. Evaluation Board Layout

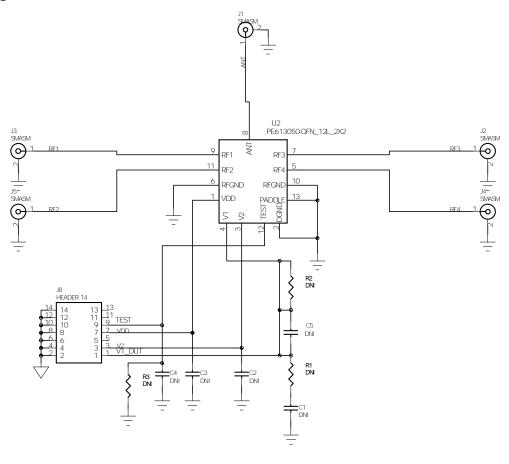

Figure 6. Evaluation Board Schematic

DOC-32627

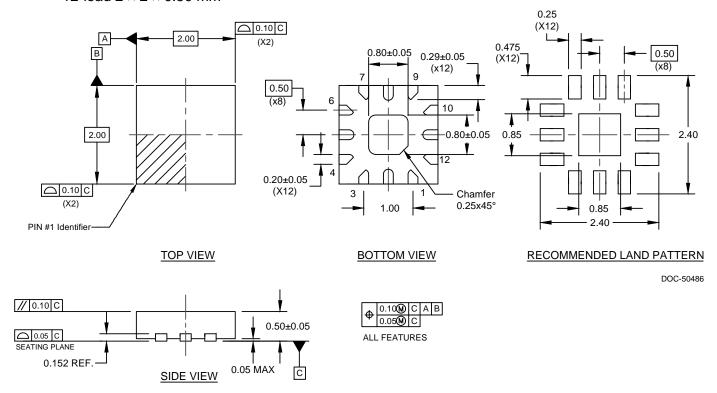

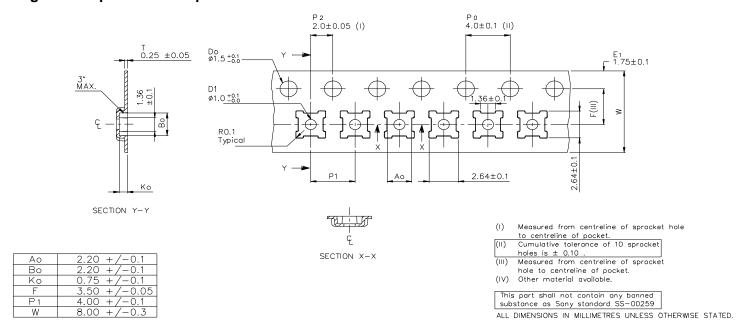

Figure 7. Package Drawing 12-lead  $2 \times 2 \times 0.50$  mm

Notes: 1. Dimensions are in millimeters.

2. Dimensions and tolerances per ASME Y14.5M, 1994.

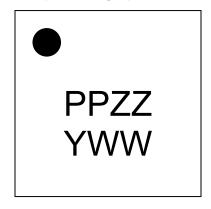

Figure 8. Top Marking Specifications

DOC-51207

| Marking Spec<br>Symbol | Package<br>Marking | Definition                                                            |

|------------------------|--------------------|-----------------------------------------------------------------------|

| PP                     | DS                 | Part number code for PE613050                                         |

| ZZ                     | 00–ZZ              | Last two characters of lot code                                       |

| Υ                      | 0–9                | Last digit of year, starting from 2009 (0 for 2010, 1 for 2011, etc.) |

| <b>WW</b> 01–53        |                    | Work week                                                             |

Note: (PP), the package marking specific to the PE613050, is shown in the figure instead of the standard Peregrine package marking symbol (P).

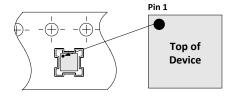

Figure 9. Tape and Reel Specifications

------ Tape Feed Direction ------

**Device Orientation in Tape**

**Table 8. Ordering Information**

| Order Code                              | Package        | Description                   | Shipping Method   |  |

|-----------------------------------------|----------------|-------------------------------|-------------------|--|

| PE613050A-Z 12-lead QFN 2 × 2 × 0.50 mm |                | Package Part in Tape and Reel | 3,000 units / T&R |  |

| EK613050-01                             | Evaluation Kit | Evaluation Kit                | 1 set / box       |  |

#### **Sales and Contact Information**

For sales and contact information please visit www.psemi.com.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. Product Specification: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp. Peregrine products are protected under one or more of the following U.S. Patents: <a href="http://patents.psemi.com">http://patents.psemi.com</a>.

# **Document Categories**

#### **Advance Information**

The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

# **Preliminary Specification**

The datasheet contains preliminary data. Additional data may be added at a later date, pSemi reserves the right to change specifications at any time without notice in order to supply the best possible product.

## **Product Specification**

The datasheet contains final data. In the event pSemi decides to change the specifications, pSemi will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

#### Sales Contact

For additional information, contact Sales at sales@psemi.com.

#### **Disclaimers**

The information in this document is believed to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the pSemi product could create a situation in which personal injury or death might occur. pSemi assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### **Patent Statement**

pSemi products are protected under one or more of the following U.S. patents: patents.psemi.com

## Copyright and Trademark

©2018, pSemi Corporation, a Murata company. All rights reserved. The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.