# Soldering Guidelines for Mounting Bottom-terminated Components

# **Application Note 62**

# Objective

The objective of this application note is to provide Peregrine Semiconductor customers with general guidelines for soldering and assembly of quad flat pack—no leads (QFNs) and other bottom-terminated components (BTCs). Precise process development and designed experimentation are needed to optimize specific application/performance.

# Introduction

QFNs are thermally enhanced plastic leadless packages with electrical connections made via lands on the bottom side of the component to the surface of the connecting substrate (PCB, ceramic, LTCC, etc.). Reflow soldering of surface mount assemblies provides mechanical, thermal and electrical connections between the component leads or terminations and the substrate surface mount land pattern. Solder paste may be applied to the surface mount lands by various methods, such as screen printing and stencil printing. Peregrine Semiconductor packages are categorized as surface mount components (SMCs). Unlike through-hole components, SMCs rely entirely upon the solder interface for mechanical strength. The solder joint properties, design and reflow process are of critical importance for successful assembly. Figure 1 shows the top side and bottom side of the QFN package.

Figure 1 • QFN Top Side and Bottom Side

Top Side

**Bottom Side**

www.psemi.com

## PC Board Land Pattern

Please refer to the Peregrine datasheet for the recommended land pattern for the package terminal pads and the center slug. **Figure 2** shows an example of a QFN land pattern. Users have the option to either use solder mask defined (SMD) pads or non-solder mask defined (NMSD) pads. High temperature FR-4 or BT laminate (glass transition temperature Tg = +170 °C to +185 °C) is generally recommended for lead-free QFN assembly. The peak lead-free reflow temperatures range from +245 °C to +260 °C using a lead-free alloy such as SAC 305 (Sn96.5Ag3.0Cu0.5%). The QFN package is also solderable with eutectic (tin/lead solder paste Sn63Pb37 alloy) at a peak reflow temperature of +225 °C to +230 °C. Please follow board design requirements based in IPC A-600—Acceptability of Printed Circuit Boards<sup>(1)</sup> and IPC 6012D—Qualification and Performance of Rigid Printed Boards<sup>(2)</sup>.

Figure 2 • QFN Land Pattern

#### **PCB Surface Finish**

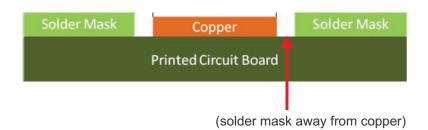

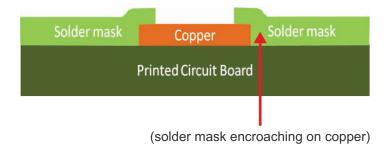

Electroless nickel/electroless palladium/immersion gold (ENEPIG) is the preferred surface finish for the PCB copper land and pads. Electroless nickel/immersion gold (ENIG), organic solderability preservative (OSP) coating over copper land pads if used for cost tradeoffs should be carefully evaluated for solder joint reliability post reflow prior to manufacturing release. In general, NSMD pads are preferred over SMD pads for all LGA packages. However, selection of NSMD versus SMD should be based on complexity of the board design and board suppliers' capability for solder mask registration and tolerance. Solder mask is recommended between all pads. The NSMD pads are illustrated in Figure 4.

Figure 3 • NSMD Pads

Figure 4 • SMD Pads

# **Solder Paste Printing**

#### **Solder Paste**

The solder paste is the vehicle that provides the flux and solder alloy necessary for a reliable and consistent assembly process. A low residue, no-clean solder paste (eutectic Sn63/Pb37 or lead-free SAC305/405 alloy SnAgCu) is commonly used. A water-soluble paste can be used if the residue can be adequately cleaned from underneath the package. Typically, the choice of solder paste determines the profile and reflow parameters. Most solder paste manufacturers provide a suggested thermal profile for their products and must be referenced prior to manufacturing. This thermal profile should also be used to meet the moisture sensitivity level (MSL) guidelines for the package per IPC/JEDEC J-STD 020E—Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices<sup>(3)</sup>.

Solder paste is typically composed of three major constituents: solder alloy powder, vehicle system and flux system. The vehicle system primarily acts as a carrier for the alloy powder, a compatible matrix for the flux system and a basis for desirable rheology. The flux cleans the alloy powder and the substrates to be joined, and facilitates wetting and formation of the solder joint.

The flux is classified based on its activity level and chemical nature, namely rosin-based (RMA), water-soluble or no-clean. Water-soluble flux is designed so that its residue after soldering can be removed using pure water or water with saponifier or an additive. No-clean solder paste is designed to not require cleaning after it is reflowed. The amount of residue left behind is often designed to not interfere with bed of nails/pin tests (shorts/open electrical test) and is non-tacky. Please refer to *Surface Mount Technology: Principles and Practices*<sup>(4)</sup>.

#### Lead-free Solders

The European Union RoHS/REACH environmental directives have required an industry-wide conversion from lead-based solders to lead-free. Lead-based solders are now being replaced by lead-free solders for both package and second-level assembly. The most common replacements for 63Sn37Pb (eutectic melt temperature +183 °C) are 96.5Sn3Ag0.5Cu (SAC305) and 96.5Sn4Ag0.5Cu (SAC405) solders, which have a eutectic point of +217 °C. Due to the non-uniformity of heat distribution on boards during reflow, the SAC solders reflow profile contains a peak temperature of +250 °C. The peak can be as high as +260 °C depending on the assembler's equipment and process capability. The high peak temperatures can cause a multitude of problems such as delamination at interfaces, external cracking, solder extrusion, etc. An optimized reflow profile and controlled ramp and cool down

are essential for reliable assemblies. Please refer to *Surface Mount Technology: Principles* and *Practices*<sup>(4)</sup>.

### **Solder Stencils**

The formation of consistent solder joints is a requirement for good assembly yields. The contrast between a large exposed pad and the small lead fingers of the QFN package can present a challenge in producing an even standoff height, so careful consideration should be given to an optimized stencil design.

The stencil thickness, as well as the stencil opening geometry, determines the precise volume of solder paste deposited onto the device land pattern. Stencil alignment accuracy and consistent solder volume transfer are critical for uniform reflow soldering.

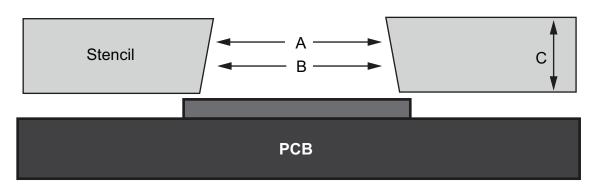

Stencils are usually made of nickel buildup or stainless steel. The nickel buildup stencil offers smoother side walls over a laser cut stainless steel stencil. Apertures are typically trapezoidal, which helps to ensure uniform release of solder paste and reduce smearing as shown in **Figure 5**. Thickness of stencils used in manufacturing varies from 0.100 mm to 0.150 mm (0.004 inch to 0.006 inch) in range, with a typical 0.125 mm (0.005 inch) stencil design for 0.5 mm pitch components. The actual thickness of the stencil is dependent on other surface mount devices on the PCB, in addition to the area and aspect ratio of the minimum aperture used.

A squeegee with a durometer of 95 or harder (such as stainless steel) is typically used to transfer the paste from the stencil to the board land pattern. The blade angle and speed must be fine-tuned to ensure even solder paste transfer. An inspection of the printed solder paste is recommended before parts placement. A repeatable brick-shaped solder deposit is the most important factor for robust reflow yields. Please refer to IPC-7525—Stencil Design Guidelines<sup>(5)</sup>.

Figure 5 • Solder Stencil Profile (Side View)

Stencil apertures should be tapered to produce more uniform release of solder paste.

## **Termination Pad Stencil Design**

The stencil aperture for the terminal fingers is typically designed to match the PCB/substrate pad size 1:1. For fine pitch components of 0.5 mm pitch and below, it may be necessary to reduce the stencil aperture by 20% to prevent shorting beneath the QFN. Please refer to the aspect ratio and area ratio requirements outlined in IPC-7525—Stencil Design Guidelines<sup>(5)</sup> for adequate print volume and board design.

The area ratio of the stencil is critical for the printing to get good paste release. For very small apertures where the area ratio is less than 0.66 mm, the stencil must be nickel formed. This type of stencil has better release characteristics over stencils that are laser etched. Please check with your stencil manufacturer for recommendations when designing an aperture with unique requirements.

Aspect Ratio = Width of Aperture Opening/Stencil Foil Thickness = W/T

Area Ratio = Area of Aperture Opening/Area of Aperture Walls = W × L / 2 × (L+W) × T

The aspect ratio relates to the manufacture of stencils. Stencil manufacturers require the aspect ratio to be >1.5 (see IPC-7525—Stencil Design Guidelines<sup>(5)</sup>). The higher the area ratio the better the solder paste release, in addition to depositing more volume. Stencil thickness is inversely proportional to the area ratio. The thinner the stencil the higher the area ratio will be, resulting in a robust solder paste release.

## **Exposed Pad Stencil Design**

The QFN package is thermally and electrically efficient due to the exposed die attach pad on the underside of the package. The exposed pad should be soldered down to the PCB.

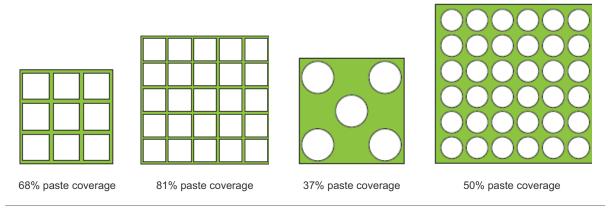

It is a good practice to minimize voids within the exposed pad interconnection, so the design of the exposed pad stencil is crucial. The proposed stencil design enables out gassing of the solder paste during reflow and also regulates the finished solder thickness. Typically, the stencil apertures are reduced such that the solder paste coverage is 50% to 70% of the exposed pad area. Designing an aperture that prints solder 1:1 with the exposed pad results in excessive paste volume that will *float* or *skate* the part causing electrical opens and other manufacturing defects. The amount of voiding post reflow in the thermal pad should not exceed 25% per IPC-A-610—*Acceptability of Electronic Assemblies*<sup>(6)</sup>. It is recommended that presence and amount of voids are checked using X-rays post reflow.

If there are thermal vias in the board exposed pad area, it is recommended that these are plugged. If plugging the via is not feasible, tenting with solder mask is another viable option. Please work with your PCB supplier to come up with the most effective plugging process. Figure 6 shows the stencil reductions.

Figure 6 • Stencil Aperture (Opening) Reduction Options

Note: \* 50-70% solder paste coverage preferred.

# Package Placement and Alignment

The pick and place machine vision accuracy governs the package placement and rotational (theta) alignment. This is equipment/process dependent. Slightly misaligned parts (less than 50% off the pad center) automatically self-align during reflow due to pullback of the solder.

Grossly misaligned packages (greater than 50% off pad center) must be removed prior to reflow as they may cause solder bridges and develop shorts.

A starting placement force of 1.5N or higher should be selected based on the manufacturer's recommendations. Once the placement force is selected, all four sides of the QFN/surface mount technology (SMT) package should be inspected to ensure that each side is seated in the solder paste. Excessive pressure can cause shorting due to solder squeeze out from underneath the part. Excessive bending of the substrate may also lead to package damage and should be avoided in the assembly flow. If the package is not making proper contact with the solder paste it can result in solder *opens* post reflow.

# **Reflow Specifications**

The reflow profile is a critical part of the PCB assembly process. A proper reflow profile must provide adequate time for flux activation and volatilization, proper peak temperature, time above liquidus, ramp up and cool down rates. The profile used has direct bearing on manufacturing yields, solder joint integrity and the reliability of the assembly. During mass soldering, it is important that all solder joints reach the minimum soldering (reflow) temperature to assure metallurgical bonding of the solder alloy and the base metals to be soldered. Metallurgical bonding requires that both surfaces to be soldered, as well as the solder, reach this minimum soldering temperature for a sufficient time to allow the wetting of the solder surfaces. For reflow profile guidelines, please refer to IPC 7530—Guidelines for Temperature Profiling for Mass Soldering Processes (Reflow & Wave)<sup>(7)</sup>.

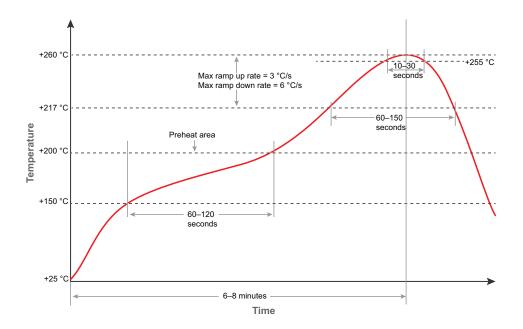

A typical reflow profile is made up of four distinct zones, the preheat zone, the soak zone/flux activation zone, the reflow zone and the cooling zone. For moisture sensitive parts, please follow the reflow guidelines in IPC/JEDEC-STD 020E—*Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices*<sup>(3)</sup>.

It is important that profiles are checked on all new board designs for critical SMT components. If there are multiple packages on the board, the reflow profile should be checked at different locations on the board.

Specific production reflow ovens and rework systems vary depending on manufacturer and model. Therefore, system specific profile must be established using a profiler and thermocouples at the actual solder joint locations or top of the package.

It is recommended that the maximum reflow temperature specified for the solder paste not be exceeded and paste manufacturer's recommendations are followed to optimize the flux activity during preheat, soak and reflow.

#### **Preheat Zone**

Typically the heating rate in the preheat zone should be +2–4 °C/second and the peak temperature in this zone should be +150–200 °C. If the temperature ramp is too fast, the solder paste may splatter and cause formation of solder balls. Also, to avoid thermal shock to sensitive components such as ceramic chip resistors, the maximum heating rate should be controlled.

#### Soak Zone

The soak zone is intended to allow the board and components to reach uniform temperature, minimizing thermal gradients. The soak zone also acts to activate the flux within the solder paste; the ramp rate in this zone is very low and the temperature is raised near the melting point of the solder (+183 °C for standard 63Sn37PB solder and +217 °C for SAC305/405 solder). If very high temperatures are used in the soak zone, the flux evaporates very quickly, resulting in solder balls. If the ramp rate is too slow, there is excessive oxidation of the solder paste, resulting in solder splatter. Typical soak times are usually around the range of +150–200 °C for 60–90 seconds.

#### **Reflow Zone**

In this zone the temperature is kept above the melting point of the solder for 30–60 seconds. The peak temperature in the zone should be high enough for adequate flux activity and to obtain good wetting. For eutectic 63Sn37Pb solders, a peak temperature range of +215–220 °C is generally considered acceptable. For lead-free solders SAC305/405, this range goes up to +250–260 °C.

The temperature, however, should not be so high as to cause component damage, board damage, discoloration or charring of the board. Extended duration above the solder melt temperature will damage temperature-sensitive components and possibly create extensive intermetallic growth between the solder and the pad metallization, which makes the solder joint brittle and reduces solder joint fatigue resistance. Additionally, high temperature can promote oxide growth depending upon the oven atmosphere, which can degrade solder wetting. Nitrogen reflow is recommended, but not required. The board and component temperature should be monitored during reflow to ensure that sufficient heat flow is present to form the joint. This can be achieved by attaching thermocouples at the top of the package and the board surface and using the profiler to monitor temperatures and ramp rates. A reflow profile for each assembly should be developed and a first article inspection conducted on the solder joints prior to committing the entire lot to assembly. Please refer to IPC-A-610— Acceptability of Electronic Assemblies<sup>(6)</sup> for solder joint inspection. For inspection of voids, typically, transmissive X-ray is used.

# **Cooling Zone**

The cooling rate of the solder joint after reflow is also important. For a given solder system, the cooling rate is directly associated with the resulting microstructure, which, in turn, affects the mechanical behavior of the solder joints. The faster the cooling rate the smaller the grain size of the solder joint will be, and hence the higher the fatigue resistance of the solder joint. Conversely, rapid cooling will result in residual stresses between coefficients of thermal expansion (CTE) mismatched components. Therefore, the cooling rate needs to be optimized.

# **Reflow Profile Example**

Figure 7 provides an example of a typical lead-free reflow profile.

Figure 7 • Lead-free Reflow Profile

# **Solder Joint Inspection**

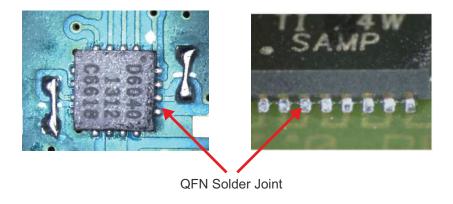

Post-reflow solder joint inspection is conducted using optical inspection to look for solder joint profile, shorts, misalignment, etc. X-ray inspection is recommended to evaluate and quantify voids in the center slug and terminal pads.

**Figure 8** shows an example of a soldered QFN and the side views of a QFN solder joint. For solder joint acceptance criteria, please refer to IPC-A-610—*Acceptability of Electronic Assemblies*<sup>(6)</sup>.

Figure 8 • QFN Solder Joint

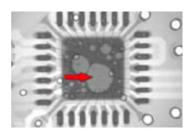

Figure 9 shows the X-ray image of a QFN package showing voids in the center pad.

Figure 9 • X-ray Image Solder Voids

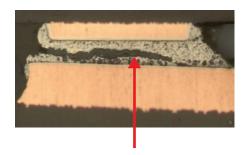

Figure 10 shows the optical image of a cracked solder joint.

Figure 10 • Cracked Solder Joint

# **PCB Cleaning**

If a low residue, no-clean solder paste is used, PCB cleaning is typically not required. No clean fluxes and solders have been formulated to minimize the harmful effects the residues left on the board may cause in the form of corrosion. There is a wide variety of no-clean solder pastes available in the market; it is recommended that application-specific evaluations be performed to identify if any remaining residue can cause harm to the assembly. Please contact your solder paste supplier for testing performed and recommended use conditions. The cleaning process for water soluble fluxes should be evaluated with special attention given to cleaning under low standoff QFN/SMT components; it is recommended that users discuss cleaning material interactions with their supplier prior to cleaning. In addition to cleaning, the drying of PC boards of any residual cleaning medium such as saponifier should be considered to prevent potential issues such as corrosion.

## Rework

The rework of lead-free solder joints can be challenging and requires proper optimization of the placement and reflow processes. Hand rework using a soldering iron is not recommended. Component removal and replacement should be done using a tool with a hot air nozzle and the ability to conduct board preheat. Proper process controls and shielding should be used to minimize impact to near neighbor components on the board and prevent their reflow. Please follow general guidelines in IPC-7093—*Guidelines for Design and Assembly Implementation for Bottom Termination Components*<sup>(8)</sup>.

The basic elements of the rework process are as follows:

- · PC board preheat

- Reflow component solder

- · Vacuum removal of component

- Cleaning and prep of PCB lands (site redressing)

- · Screen print paste on lands

- · Placement and reflow of new component

- Inspection of solder joints

## **PC Board Preheat**

Board preheat is required for lead-free rework to ensure that the board is heated properly prior to solder melt. Component removal by topside heat only can result in lifted lands. The board should be preheated at a temperature of +90–125 °C. Board preheat ensures that the board is in equilibrium before the solder melts. Baking of PCBs for moisture removal should be done using time and temperatures recommended by the PCB board supplier. This bake operation should be conducted prior to board preheat and is recommended to prevent delamination and damage to other components. Please refer to IPC-7711B/21B—Rework, Modification and Repair of Electronic Assemblies<sup>(9)</sup>.

## Reflow/Removal of the Component from PCB

It is recommended that a hot gas nozzle be used for localized component rework to minimize impact to near neighbor components on the board. These nozzles incorporate a hot gas shroud that heats up the part to a temperature required for reflowing the solder interconnects. Once the solder reflows, the nozzle vacuum cup automatically lifts the unit from the PCB. The nozzle size and heat flow should be optimized to keep the heat flow localized. Parts must not exceed the peak temperature listed on the MSL label for the package. Reuse of the part after it is removed is not recommended.

## Site Redressing of the PCB Land

After removal of the component, the PCB can be cleaned and prepped using conventional tools and cleaning processes used for SMT packages. To avoid damaging the board pads or solder mask, the site redress process must be performed with caution. Flux is applied to the site after component removal. Residual solder remaining on the board pad can be removed using a solder wick soaked in flux. Using a temperature-controlled soldering iron fitted with a flat blade, gently place solder wick on the PCB lands to facilitate removal of solder residue. Residual flux can be removed from the site with alcohol and a lint-free swab. The site should then be inspected prior to the component replacement process.

## **Screen Printing of Solder Paste**

Due to the tight geometries used on today's PC boards, it is difficult to screen print paste on the assembled board. Hence, the approach of screen printing the paste directly on the new component using a mini-stencil has been adopted. It is recommended to use a type 3 or type 4 no-clean solder paste.

# Placement and Reflow of the Component

The placement of the SMT component should be done with an optical split prism system combined with a microscope. The image of the screen printed component and the PCB land pattern are superimposed during the placement and alignment operation. Once the package is correctly aligned, the X–Y table is locked to prevent further movement. The reflow of the new component is done with localized hot air reflow. Once the cool down stage is complete, the nozzle is raised and the assembly is removed for inspection. The rework profile should have the ramp rates and peak temperatures similar to the initial reflow and follow the guidelines of component handling specified in J-STD-033C—Handling, Packing, Shipping and Use of Moisture /Reflow Sensitive Surface Mount Devices<sup>(10)</sup>.

# Soldering Guidelines for BTCs

Notes: (References)

- 1) IPC-A-600—Acceptability of Printed Circuit Boards

- 2) IPC-6012D—Qualification and Performance of Rigid Printed Boards

- 3) J-STD-020E—Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices

- 4) Surface Mount Technology: Principles and Practices by Ray Prasad

- 5) IPC-7525—Stencil Design Guidelines

- 6) IPC-A-610—Acceptability of Electronic Assemblies

- 7) IPC-7530—Guidelines for Temperature Profiling for Mass Soldering Processes (Reflow and Wave)

- 8) IPC-7093—Guidelines for Design and Assembly Implementation for Bottom Termination Components

- 9) IPC-7711B/21B—Rework, Modification and Repair of Electronic Assemblies

- 10) J-STD-033C—Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices

#### **Sales Contact**

For additional information, contact Sales at sales@psemi.com.

#### **Disclaimers**

The information in this document is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### **Patent Statement**

Peregrine products are protected under one or more of the following U.S. patents: patents.psemi.com

## **Copyright and Trademark**

©2016, Peregrine Semiconductor Corporation. All rights reserved. The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.