# **Product Description**

The PE42430 is a HaRP<sup>™</sup>-enhanced reflective SP3T RF switch developed on the UltraCMOS<sup>®</sup> process technology. This tiny general purpose switch is ideal for WLAN and bluetooth applications in the 2.4 - 2.5 GHz bands as well as general broadband switching applications. It is comprised of three RF ports and has low insertion loss and high isolation. An on-chip CMOS decode logic facilitates a three-pin CMOS control interface. Unlike competitive solutions, there is no need for blocking capacitors when using the PE42430.

pSemi's HaRP<sup>™</sup> technology enhancements deliver high linearity and exceptional harmonics performance. It is an innovative feature of the UltraCMOS<sup>®</sup> process, providing performance superior to GaAs with the economy and integration of conventional CMOS.

# Product Specification PE42430

UltraCMOS<sup>®</sup> SP3T Reflective RF Switch 100 – 3000 MHz

### Features

- HaRP<sup>™</sup>-enhanced UltraCMOS<sup>®</sup> device

- Low insertion loss

- Typical 0.45 dB @ 1 GHz

- Typical 0.55 dB @ 2.5 GHz

- IIP3: Typical +66 dBm

- P0.1dB Compression: Typical +30 dBm

- Excellent ESD tolerance of 4500V HBM and 250V MM on all ports

- No external V<sub>DD</sub> required. V<sub>DD</sub> is derived from switch control inputs

- Package type: 8-lead 1.5 x 1.5 mm DFN

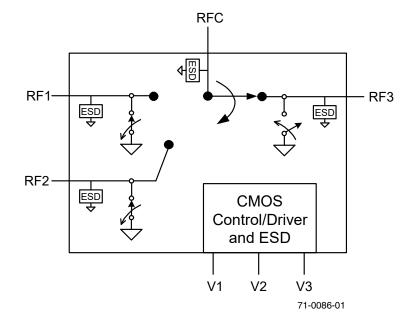

Figure 1. Functional Diagram

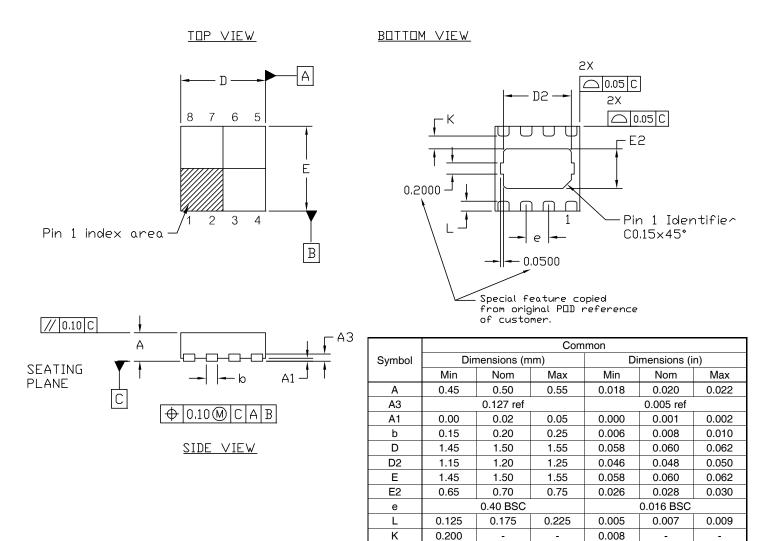

Figure 2. Package Type 8-lead 1.5 x 1.5 mm DFN

# Table 1. Electrical Specifications<sup>1</sup>: Nominal @ 25°C, V1, V2 or V3 = 3V/5V (Z<sub>s</sub> = Z<sub>L</sub> = 50 $\Omega$ )

| <b>Electrical Parameter</b>           | Path    | Condition                             | Min | Тур  | Max  | Unit |

|---------------------------------------|---------|---------------------------------------|-----|------|------|------|

| Operating Frequency                   |         |                                       | 100 |      | 3000 | MHz  |

| Insertion Loss                        |         | 100 to 1000 MHz                       |     | 0.45 | 0.56 | dB   |

|                                       | RFC-RFX | 1000 to 3000 MHz                      |     | 0.65 | 0.9  | dB   |

|                                       |         | 2400 to 2500 MHz                      |     | 0.55 | 0.8  | dB   |

| Isolation                             |         | 100 to 1000 MHz                       | 35  | 40   |      | dB   |

|                                       | RFX-RFX | 1000 to 3000 MHz                      | 23  | 28   |      | dB   |

|                                       |         | 2400 to 2500 MHz                      | 25  | 30   |      | dB   |

| Isolation                             |         | 100 to 1000 MHz                       | 34  | 40   |      | dB   |

|                                       | RFC-RFX | 1000 to 3000 MHz                      | 23  | 28   |      | dB   |

|                                       |         | 2400 to 2500 MHz                      | 25  | 30   |      | dB   |

| Return Loss (Active Port)             |         | 100 to 1000 MHz                       |     | 22   |      | dB   |

|                                       | RFX     | 1000 to 3000 MHz                      |     | 16   |      | dB   |

|                                       |         | 2400 to 2500 MHz                      |     | 18   |      | dB   |

| Return Loss (Common Port)             |         | 100 to 1000 MHz                       |     | 22   |      | dB   |

|                                       | RFC     | 1000 to 3000 MHz                      |     | 16   |      | dB   |

|                                       |         | 2400 to 2500 MHz                      |     | 18   |      | dB   |

| Input 0.1 dB compression <sup>2</sup> | RFC-RFX | 100 to 3000 MHz                       |     | 30   |      | dBm  |

| IIP3                                  | RFC-RFX | 100 to 3000 MHz                       |     | 66   |      | dBm  |

| IIP2                                  | RFC-RFX | 100 to 3000 MHz                       |     | 100  |      | dBm  |

| Switching Time <sup>3</sup>           |         | 50% CTRL to 90% or 10% of final value |     | 500  |      | nS   |

| Turn on Time <sup>4</sup>             |         | 50% CTRL to 90% or 10% of RF          |     | 1.5  | 2.0  | μS   |

| Video Feedthrough <sup>5</sup>        |         |                                       |     | 10   |      | mV   |

Notes: 1. Specifications under min and max nominal conditions

2. Please refer to Maximum Input Power (50  $\Omega$  ) in Table 4.

3. Switching time is measured while the part is powered on and one of the control pins is switching state.

4. Turn on time is defined as the time it takes the part to go from an unpowered state to 90% RF voltage. Max power

can only be applied after the part is turned on/

5. Video feedthrough is measured by terminating all ports and measuring peak transients while switching logic state.

# Table 3. Electrical Specifications: Min/Max Performance @ -40 to +85°C, V1, V2 or V3 = 3.0V to 5.5V $(Z_s = Z_L = 50 \Omega)$

| Electrical Parameter | Path    | Condition        | Min | Тур  | Max  | Unit |

|----------------------|---------|------------------|-----|------|------|------|

| Operating Frequency  |         |                  | 100 |      | 3000 | MHz  |

| Insertion Loss       |         | 100 to 1000 MHz  |     | 0.45 | 0.65 | dB   |

|                      | RFC-RFX | 1000 to 3000 MHz |     | 0.65 | 0.95 | dB   |

|                      |         | 2400 to 2500 MHz |     | 0.55 | 0.85 | dB   |

| Isolation            |         | 100 to 1000 MHz  | 35  | 40   |      | dB   |

|                      | RFX-RFX | 1000 to 3000 MHz | 23  | 28   |      | dB   |

|                      |         | 2400 to 2500 MHz | 25  | 30   |      | dB   |

| Isolation            |         | 100 to 1000 MHz  | 34  | 40   |      | dB   |

|                      | RFC-RFX | 1000 to 3000 MHz | 23  | 28   |      | dB   |

|                      |         | 2400 to 2500 MHz | 25  | 30   |      | dB   |

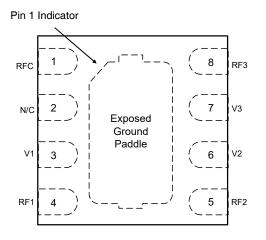

# Figure 3. Pin Configuration (Top View)

#### **Table 3. Pin Descriptions**

| Pin #  | Pin Name         | Description                                                  |

|--------|------------------|--------------------------------------------------------------|

| 1      | RFC*             | RF Common                                                    |

| 2      | N/C              | No Connect                                                   |

| 3      | V1               | Switch Control Input, CMOS logic level                       |

| 4      | RF1*             | RF I/O                                                       |

| 5      | RF2*             | RF I/O                                                       |

| 6      | V2               | Switch Control Input, CMOS Logic Level                       |

| 7      | V3               | Switch Control Input, CMOS Logic Level                       |

| 8      | RF3 <sup>1</sup> | RF I/O                                                       |

| Paddle | GND              | Exposed Ground Paddle. Ground for<br>Proper Device Operation |

Note \*: RF pins 1, 4, 5 and 8 must be at 0 VDC. The RF pins do not require DC blocking capacitors for proper operation if the 0 VDC requirement is met.

#### **Table 4. Operating Ranges**

| Parameter                                              | Symbol          | Min | Тур | Max        | Units      |

|--------------------------------------------------------|-----------------|-----|-----|------------|------------|

| IDD Power Supply Current                               | I <sub>DD</sub> |     | 130 | 230        | μA         |

| V <sub>CTRL</sub> Control Voltage High                 | V <sub>IH</sub> | 3   |     | 5.5        | v          |

| V <sub>CTRL</sub> Control Voltage Low                  | V <sub>IL</sub> | 0   |     | 0.6        | v          |

| Operating temperature range                            | T <sub>OP</sub> | -40 |     | +85        | °C         |

| Maximum Input Power (50 Ω)<br>CW @ +85°C<br>CW @ +25°C | P <sub>in</sub> |     |     | +27<br>+30 | dBm<br>dBm |

#### **Table 5. Absolute Maximum Ratings**

| Symbol           | Parameter/Conditions                   | Min | Max  | Units |

|------------------|----------------------------------------|-----|------|-------|

| T <sub>ST</sub>  | Storage temperature range              | -55 | +150 | °C    |

| P <sub>IN</sub>  | Maximum Input Power (50 $\Omega$ )     |     | 30   | dBm   |

| $V_{\text{ESD}}$ | ESD Voltage HBM <sup>1</sup> All Pins  |     | 4500 | V     |

| V <sub>ESD</sub> | ESD Voltage MM <sup>2</sup> , All Pins |     | 250  | V     |

Notes: 1. HBM ESD Voltage (MIL\_STD 883 Method 3015.7)

2. MM ESD Voltage (MM, JEDEC JESD22-A115-A)

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS<sup>®</sup> device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE42430 in the 8-lead 1.5 x 1.5 mm DFN package

#### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS<sup>®</sup> devices are immune to latch-up.

#### Table 6. Truth Table

| Path      | V1 | V2 | V3 |

|-----------|----|----|----|

| RFC - RF1 | 1  | 0  | 0  |

| RFC - RF2 | 0  | 1  | 0  |

| RFC - RF3 | 0  | 0  | 1  |

Note: Any state other than shown in *Table 6* are undefined states.

#### **Switching Frequency**

The PE42430 has a maximum 25 kHz switching rate.

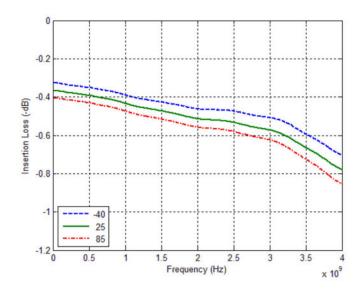

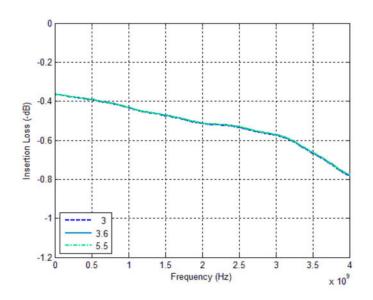

# Figure 4. Insertion Loss vs Temperature (RFX-RFC)

Figure 5. Insertion Loss vs V<sub>DD</sub> (RFX-RFC)

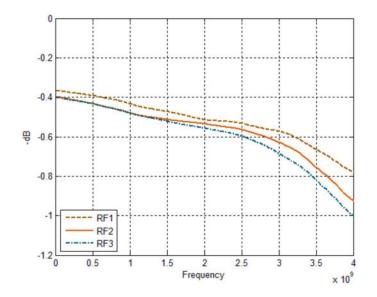

### Figure 6. Insertion Loss RFX

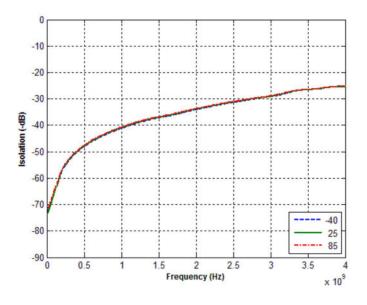

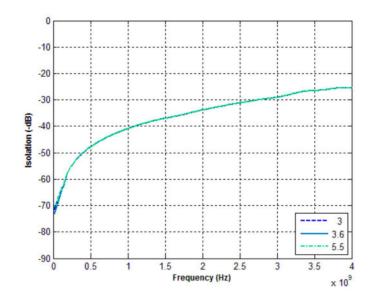

Figure 7. RFX-RFX Isolation vs Temperature

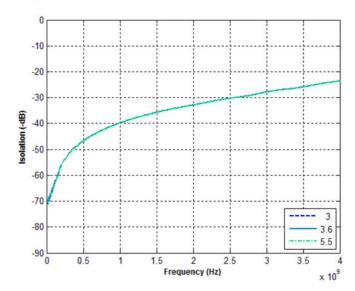

Figure 9. RFC-RFX Isolation vs Temperature

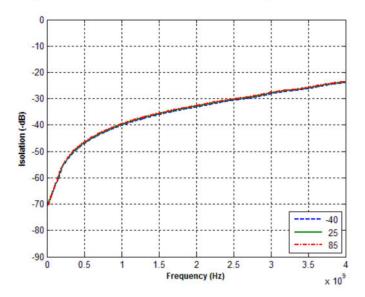

Figure 8. RFX-RFX Isolation vs V<sub>DD</sub>

Figure 10. RFC-RFX Isolation vs  $V_{\text{DD}}$

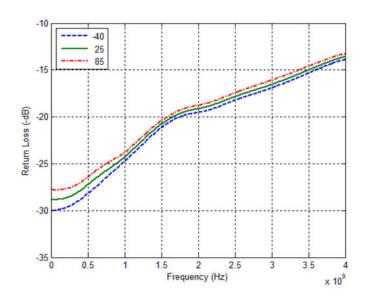

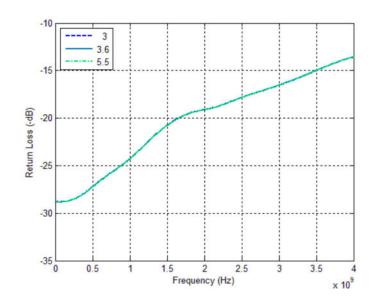

# Figure 11. RFC Port Return Loss vs Temperature

Figure 13. Active Port Return Loss vs Temperature (RFX)

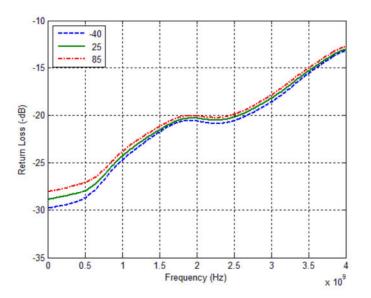

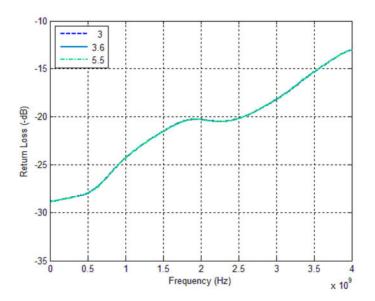

Figure 12. RFC Port Return Loss vs V<sub>DD</sub>

Figure 14. Active Port Return Loss vs V<sub>DD</sub> (RFX)

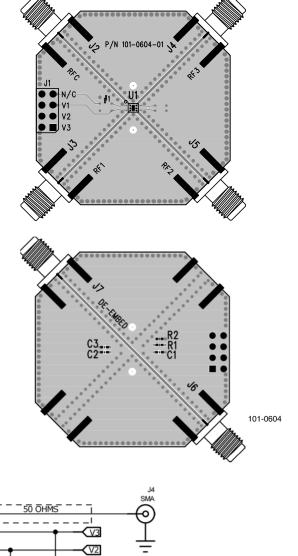

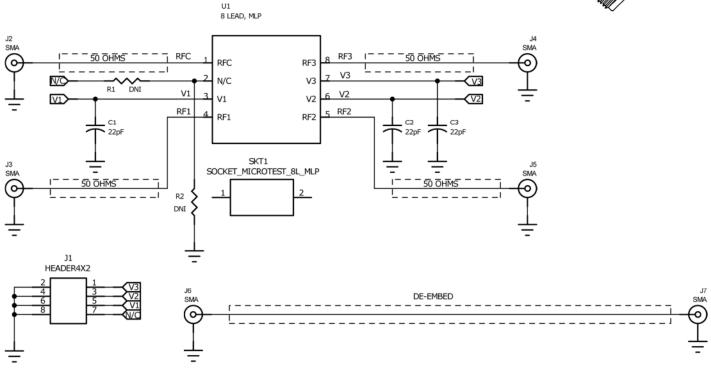

#### **Evaluation Kit Information**

The SP3T Switch Evaluation Kit facilitates customer evaluation of the PE42430 SP3T switch. The RF common port is connected through a 50  $\Omega$ transmission line to J2. Ports 1, 2 and 3 are connected through 50  $\Omega$  transmission lines to J3, J5 and J4 respectively. J1 provides digital inputs V1, V2 and V3 to the device.

On the back of the board, a through line connects SMA connectors J6 and J7. This transmission line can be used to estimate the PCB loss over the environmental conditions.

This four layer board is composed of Rogers 4350 on the top and bottom and FR4 on the inner layers with a total thickness of 0.062". All transmission lines have 21.5 mil width and 7.25 mil gap.

Use jumpers on header J1 to short the control pins to ground for logic low.  $V_{DD}$  is supplied to the part through at least one of the control pins via Pins 1, 3 or 5 (V3, V2, V1) on header J1.

#### Figure 15. Evaluation Board Layouts

#### Figure 16. Evaluation Kit Schematics

Document No. DOC-18114-2 | www.psemi.com

©2010-2023 pSemi Corporation. All rights reserved.

### Figure 17. Mechanical Specifications

#### Figure 18. Marking Specifications

| Marking Spec<br>Symbol | Package<br>Marking | Definition                                                            |  |

|------------------------|--------------------|-----------------------------------------------------------------------|--|

| Р                      | A-Z                | Part# code*                                                           |  |

| ZZ                     | 00-99              | Last two digits of lot code                                           |  |

| Y                      | 0-9                | Last digit of year, starting from 2011<br>(1 for 2011,2 for 2012 etc) |  |

| WW                     | 01-53              | Work week                                                             |  |

Note \*: The part number marking for PE42430 is D.

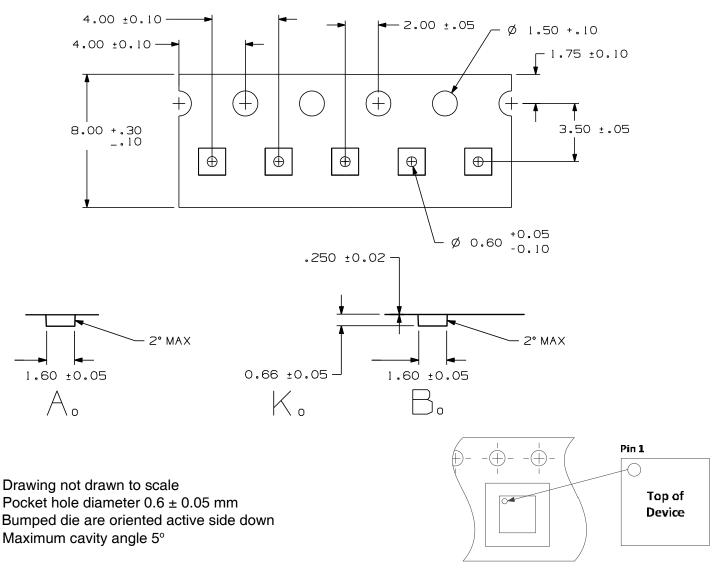

#### Figure 19. Tape and Reel Drawing

**Device Orientation in Tape**

#### **Table 7. Ordering Information**

| Order Code    | Description              | Package               | Shipping Method |  |

|---------------|--------------------------|-----------------------|-----------------|--|

| PE42430MLAB-Z | PE42430 SP3T RF Switch   | Green 8LD 1.5x1.5 DFN | 3000 units T/R  |  |

| EK42430-01    | PE42430 Evaluation board | Evaluation Kit        | 1/Box           |  |

#### **Sales Contact and Information**

For sales and contact information please visit www.psemi.com.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later date. pSemi reserves the right to change specifications at any time without notice in order to supply the best possible product. <u>Product Specification:</u> The datasheet contains final data. In the event pSemi decides to change the specifications, pSemi will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this document is believed to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

Document No. DOC-18114-2 | www.psemi.com

No patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the pSemi product could create a situation in which personal injury or death might occur. pSemi assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.

©2010-2023 pSemi Corporation. All rights reserved.