## PE29102

## **Document Category: Product Specification**

## UltraCMOS® High-speed FET Driver, 40 MHz

### **Features**

- · High- and low-side FET drivers

- · Dead-time control

- · Fast propagation delay, 9 ns

- · Tri-state enable mode

- · Sub-nanosecond rise and fall time

- · 2A/4A peak source/sink current

- · Package flip chip

## **Applications**

- · Class D audio

- DC–DCconversions

- · AC-DC conversions

- · Wireless charging

- · Envelope tracking

- LiDAR

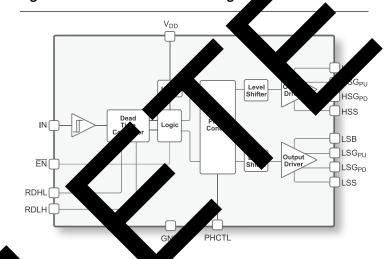

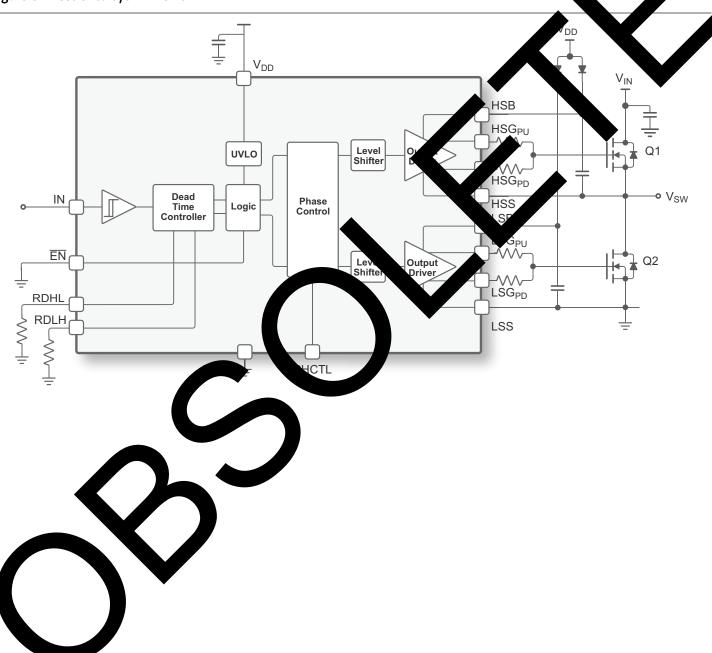

### Figure 1 • PE29102 Functional Diagram

## **Product Description**

gh-speed drive The PE29102 is an integrated to control the gates of external power devices, such FETs. The outputs of the PE29102 are capable of providing as enhancement mode galling nitride ( switching transition speeds and range for switching applications up to 40 MHz. The PE29102 is optimized for matched dead and offers est-in-class propagation delay to improve system bandwidth. High switching spe ult in smaller peri ral components and enable innovative designs for applications such as class D The PE29102 is available in a flip chip package. wireless

The PE29103 manufactor in Peregrine's UltraCMOS process, a patented advanced form of silicon-on-insulator (SOI) through y, offer the performance of GaAs with the economy and integration of conventional CMOS.

©2018, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Product Specification DOC-81227-7 – (11/2018)

## **Absolute Maximum Ratings**

Exceeding absolute maximum ratings listed in **Table 1** may cause permanent damage. Operation should be restricted to the limits in **Table 2**. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

### **ESD Precautions**

When handling this UltraCMOS device, observe the same precautions as with any other ESL censitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should aken to avoid exceeding the rating specified in **Table 1**.

### Latch-up Immunity

Unlike conventional CMOS devices, UltraCMOS devices are immune to lath-up.

Table 1 ■ Absolute Maximum Ratings for PE29102

| Parameter/Condition                            | Min  | Max | Unit |

|------------------------------------------------|------|-----|------|

| Low-side bias (LSB) to low-side source (LSS)   | -0.2 | 7   | V    |

| High-side bias (HSB) to high-side source (HSS) | .3   | 7   | V    |

| Input signal                                   | -0.3 | 7   | V    |

| HSS to LSS                                     | -100 | 100 | V    |

| HSS to GND                                     | -1   | 100 | V    |

| LSS to GND                                     | -1   | 100 | V    |

| ESD voltage HBM <sup>(*)</sup> , all pins      |      | 500 | V    |

| Note: * Human body model (JEDEC JS-2A).        | ·    |     |      |

# **Recommended Operating Conditions**

**Table 2** lists the recommended operating conditions for the PE29102. Devices should not be operated outside the recommended operating conditions listed below.

Table 2 ■ Recommended Operating Conditions for PE29102

| Parameter                                    | Min | Тур | Max  | Jnit |

|----------------------------------------------|-----|-----|------|------|

| Supply for driver front-end, V <sub>DD</sub> | 4.0 | 5.0 | 0    | V    |

| Supply for high-side driver, HSB             | 4.0 | 5.0 | 6.   |      |

| Supply for low-side driver, LSB              | 4.0 |     | 6.0  | V    |

| HIGH level input voltage, VIH                | 1.6 |     | 6.0  | V    |

| LOW level input voltage, VIL                 | 0   |     | 0.6  | V    |

| HSS range                                    | 0   |     | -0   | V    |

| LSS range                                    |     |     | 60   | V    |

| Operating temperature                        | -40 |     | +105 | °C   |

| Junction temperature                         | -40 |     | +125 | °C   |

DOC-81227-7 – (11/2018) Page 3 of 16

# **Electrical Specifications**

**Table 3** provides the key electrical specifications @ +25 °C, V<sub>DD</sub> = 5V, 100 pF load, HSB and LSB bootstrap diode included unless otherwise specified.

Table 3 ■ DC Characteristics

| Parameter                                                 | Condition                             | Min | Тур         | Max  | Jnit |

|-----------------------------------------------------------|---------------------------------------|-----|-------------|------|------|

| DC Characteristics                                        |                                       | -   |             |      |      |

| V <sub>DD</sub> quiescent current                         | V <sub>DD</sub> = 5V                  |     | .3          |      | m    |

| HSB quiescent current                                     | V <sub>DD</sub> = 5V                  |     |             |      | IA.  |

| LSB quiescent current                                     | V <sub>DD</sub> = 5V                  |     | 2.7         |      | mA   |

| Total quiescent current                                   | V <sub>DD</sub> = 5V                  |     | 6.7         | 9.0  | mA   |

| V <sub>DD</sub> quiescent current                         | V <sub>DD</sub> = 6V                  |     | 1.6         |      | mA   |

| HSB quiescent current                                     | V <sub>DD</sub> = 6V                  |     | 3.6         |      | mA   |

| LSB quiescent current                                     | V <sub>DD</sub> = 6V                  |     | 3           |      | mA   |

| Total quiescent current                                   | V <sub>DD</sub> = 6V                  |     | <b>J.</b> 0 | 11.6 | mA   |

| Under Voltage Lockout                                     |                                       |     |             |      |      |

| Under voltage release (rising)                            |                                       |     | 3.6         | 3.8  | V    |

| Under voltage hysteresis                                  |                                       |     | 400         |      | mV   |

| Gate Drivers                                              |                                       |     | 1           |      | 1    |

| HSG <sub>PU</sub> /LSG <sub>PU</sub> pull-up resistance   |                                       |     | 1.9         |      | Ω    |

| HSG <sub>PD</sub> /LSG <sub>PD</sub> pull-down resistance |                                       |     | 1.3         |      | Ω    |

| HSG <sub>PU</sub> /LSG <sub>PU</sub> leakage current      | VSG <sub>PU</sub> V LSB-LSG = 5V      |     | 10          |      | μA   |

| HSG <sub>PD</sub> /LSG <sub>PD</sub> leakage current      | HSG <sub>PD</sub> -HSS = 5V, LSS = 5V |     | 10          |      | μA   |

| Dead-time Control                                         |                                       |     | 1           |      | 1    |

| Dead-time control voltages                                | κΩ resistor GND                       |     | 1.3         |      | V    |

|                                                           | RDHL = 30 k                           |     | 1.9         |      | ns   |

| Dead-time from by going love                              | RL κΩ                                 |     | 7.0         |      | ns   |

| LSG going high                                            | PDHL = 150 kΩ                         |     | 13.6        |      | ns   |

|                                                           | DHL = 255 kΩ                          |     | 23.5        |      | ns   |

|                                                           | RDLH = 30 kΩ                          |     | 1.8         |      | ns   |

| Cond-time from Leastoing least                            | RDLH = 80.6 kΩ                        |     | 6.7         |      | ns   |

| G going high                                              | RDLH = 150 kΩ                         |     | 13.2        |      | ns   |

|                                                           | RDLH = 255 kΩ                         |     | 22.7        |      | ns   |

| Sk hing Charac istics                                     |                                       |     |             |      |      |

| LSG to gation delay                                       | At min dead time                      |     | 9.1         |      | ns   |

| HSG rise time                                             | 10 - 90% with 100pF load              |     | 0.9         |      | ns   |

| LSG rise time                                             | 10 - 90% with 100pF load              |     | 0.9         |      | ns   |

| HSG fall time                                             | 90 - 10% with 100pF load              |     | 0.8         |      | ns   |

| LSG fall time                                             | 90 - 10% with 100pF load              |     | 0.9         |      | ns   |

### Table 3 ■ DC Characteristics (Cont.)

| Parameter                                | Condition           | Min | Тур | Max | Unit |

|------------------------------------------|---------------------|-----|-----|-----|------|

| Minimum output pulse width               |                     |     | 2.8 | 5.0 | ns   |

| Max switching frequency @ 50% duty cycle | RDHL = RDLH = 80 kΩ | 40  |     |     | MHz  |

# **Control Logic**

Table 4 provides the control logic truth table for the PE29102.

Table 4 ■ Truth Table for PE29102

| EN | IN | HSG <sub>PU</sub> -HSS | HSG <sub>PD</sub> -HSS | LSG <sub>PU</sub> -LSS | LSG <sub>PD</sub> -LSS |

|----|----|------------------------|------------------------|------------------------|------------------------|

| L  | L  | Hi–Z                   | L                      | <b>→</b> H             | Hi–Z                   |

| L  | Н  | Н                      | Hi-                    | Hi–Z                   | L                      |

| Н  | L  | Hi–Z                   | L                      | Hi–7                   | L                      |

| Н  | Н  | Hi–Z                   | L                      | 1                      | L                      |

DOC-81227-7 – (11/2018) Page 5 of 16

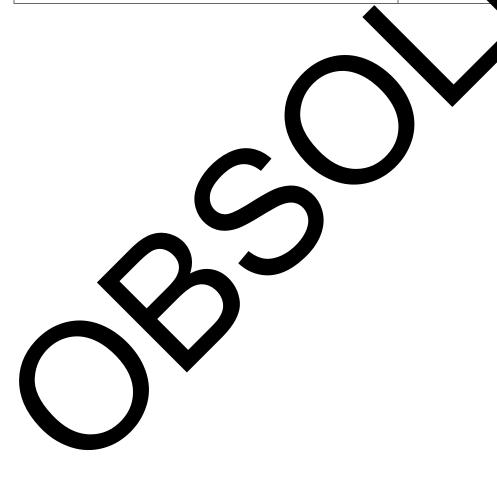

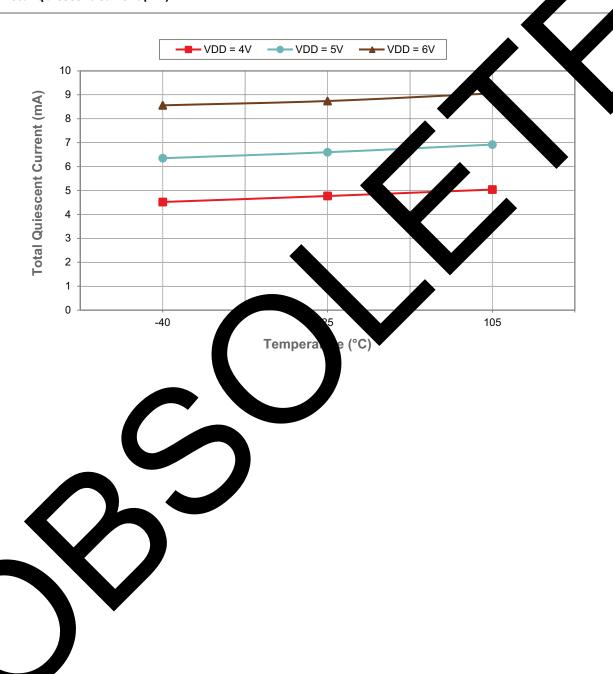

# **Typical Performance Data**

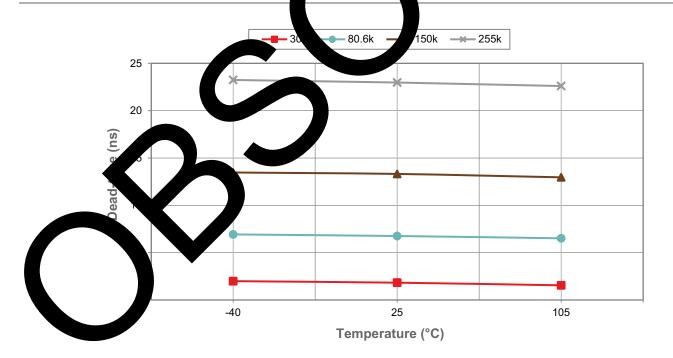

**Figure 2** through **Figure 4** show the typical performance data @ +25 °C,  $V_{DD}$  = 5V, load = 2.2Ω resistor in series with 100 pF capacitor, HSB and LSB bootstrap diode included, unless otherwise specified.

Figure 2 • Total Quiescent Current (mA)

Figure 3 • UVLO Threshold (V)

Figure 4 • Dead-time (ns)

DOC-81227-7 – (11/2018) Page 7 of 16

# **Test Diagram**

**Figure 5** shows the test circuit used for obtaining measurements. The two bootstrap diodes shown in the schematic are used for symmetry purposes in characterization. In practice, only the HSB diode is required. Removing the LSB diode will result in higher low-side supply voltage since the diode drop is eliminated. As a result, the dead-time resistor can be adjusted to compensate for any changes in propagation delta.

Figure 5 • Test Circuit for PE29102

## Theory of Operation

#### General

The PE29102 is intended to drive both the high-side (HS) and the low-side (LS) gates of external power FETs, such as enhancement mode GaN FETs, for power management applications. The PE29102 is small for applications requiring higher switching speeds due to the reduced parasitic properties of the high remarking substrate inherent with Peregrine's UltraCMOS process.

The driver uses a single-ended pulse width modulation (PWM) input that feeds a dead the country, capable of generating a small and accurate dead-time. The dead-time circuit prevents shoot cough current in the output stage. The propagation delay of the dead-time controller must be small to receive the fast switch a requirements when driving GaN FETs. The differential outputs of the dead-time controller are the level-shifts of a low-voltage domain to a high-voltage domain required by the output drivers.

Each of the output drivers includes two separate pull-up and pull-down or puts allowing independent control of the turn-on and turn-off gate loop resistance. The low impedance output of the drivers improve external power FETs switching speed and efficiency, and minimizes the effects of two voltage to time (dv/dt) transients.

### **Under-voltage Lockout**

An internal under-voltage lockout (UVLO) feature prevents the PE29102 has powering up before input voltage rises above the UVLO threshold of 3.6V (typ), and 400 V (typ) of hysteresis and ilt in to prevent false triggering of the UVLO circuit. The UVLO must be cleared and the EN pin must be released before the part will be enabled.

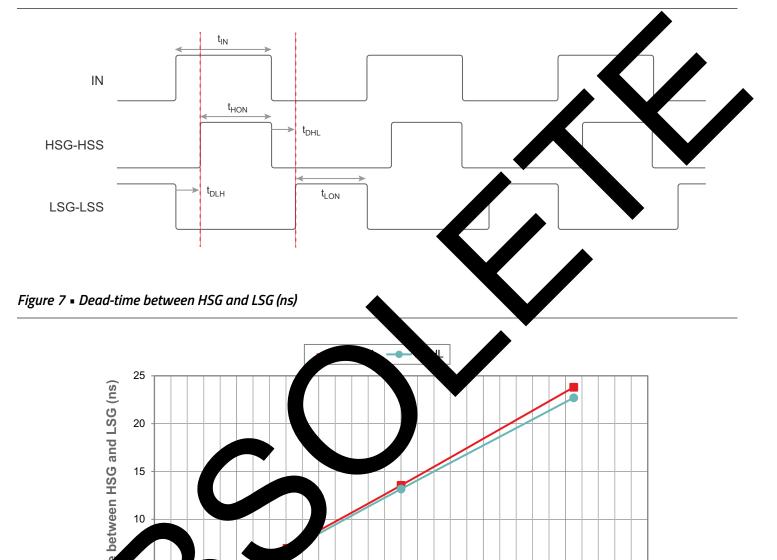

### Dead-time Adjustment

The PE29102 features a dead-time adjustment that allows to user to control the timing of the LS and HS gates to eliminate any large shoot-through current which could comatically reduce the efficiency of the circuit and potentially damage the GaN FETs. Two external resistors of trol the timing of outputs in the dead-time controller block. The timing was forms are illustrated in the damage to the controller block.

The dead-time resistors only dge of the low-side gate (LSG) and high-side gate (HSG) outputs. ffect the Dead-time resistor RDLH will ge of HSG, thus providing the desired dead-time between LSG falling and HSG rising. Likewis stor RDHL will delay the rising edge of LSG, thus providing the ad-time re desired dead-time HSG falling and G rising. Figure 7 shows the resulting dead-time versus the external resistor bias diode/capacitors installed as indicated in Figure 5. The LS lues w apacitor. ded for symmetry only and are not required for the part to function. Removing bias diode an the LS bias did  $_{ t LSG}$  voltage by approximately 0.3V, resulting in a wider separation of the  ${ t t}_{ t DHL}$ ease th and t<sub>DLH</sub> curves in re 7.

#### Plase Control

Fig. 10 (PHCTL) coursels the polarity of the gate driver outputs. When PHCTL is low, the HSG will be in phase the input signs. When PHCTL is high, the LSG will be in phase with the input signal. The PHCTL pin includes an interresponding of the polarity of the gate driver outputs. When PHCTL is low, the HSG will be in phase with the input signal. The PHCTL pin includes an interresponding of the gate driver outputs. When PHCTL is low, the HSG will be in phase with the input signal. The PHCTL pin includes an interresponding of the gate driver outputs.

DOC-81227-7 – (11/2018) Page 9 of 16

Figure 6 and Figure 7 provide the dead-time description for the PE29102.

Figure 6 • Dead-time Description

150

Dead-time Resistance (kΩ)

200

250

300

100

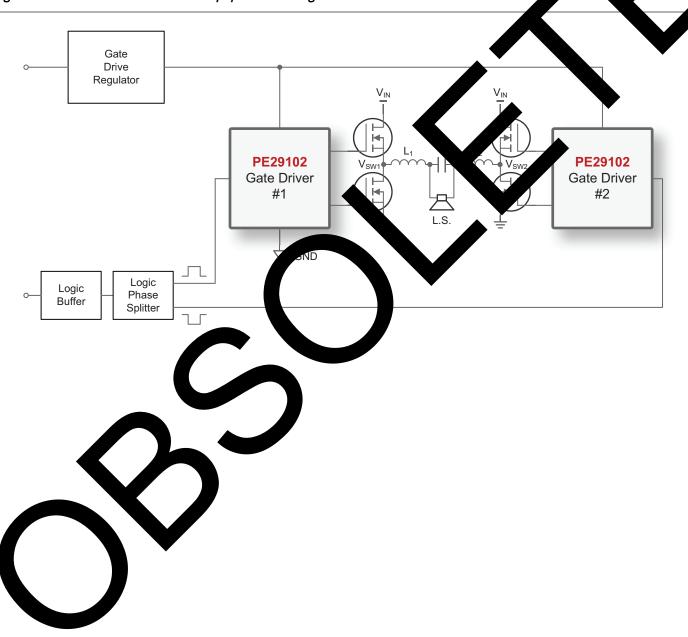

### **Application Circuit**

Figure 8 shows a class-D audio amplifier application diagram using two PE29102 gate drivers in a full-bridge configuration. The full-bridge circuit comprises two half bridge topologies that share a common supply and load. The low-level logic circuitry is powered by the gate drive regulator that supplies the PE29102 drivers ogic buffer and phase splitter. The PWM input signal feeds a single logic buffer, which drives a common logic x-OR gate Phase Splitter that provides phase inverted signals to each driver. VIN is designed to operate 50V DC (max.) to provide between 100 — 120W of power into an 8Ω load.

Figure 8 • PE29102 Class D Audio Amplifier Block Diagram

### **Evaluation Board**

The PE29102 evaluation board (EVB) allows the user to evaluate the PE29102 gate driver in either a full-bridge configuration or two independent half-bridge configurations. The EVB is assembled with two PE29102 FET drivers and four GS61004B E-mode GaN FETs. Refer to Peregrine Semiconductor DOC-82956 for mation.

Because the PE29102 is capable of generating fast switching speeds, the printed circuit boars (PCB) lay at is a critical component of the design. The layout should occupy a small area with the power FE cand extend bypass capacitors placed as close as possible to the driver to reduce any resonances a social by the gate loops, common source and power loop inductances. Since the maximum allowable of e-to-source foltage for the GS61004B FETs is 7V, resonance in the gate loops can generate ringing that the degrade the power devices due to high voltage spikes. Additionally, it is apportant to keep bound paths short.

The PCB is fabricated on FR4 material, with a total thickness of 0.062 in res. A minimum of the thickness of 1.5 ounces or more is recommended on the PCB outer layers to limit a stive losses and implice thermal spreading.

Figure 9 ■ PE29102 Evaluation Board Assembly

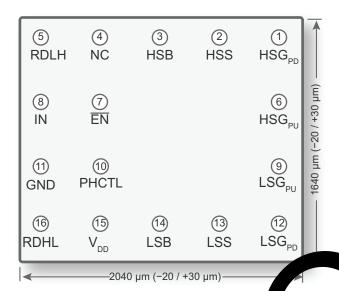

# **Pin Configuration**

This section provides pin information for the PE29102. **Figure 10** shows the pin map of this device for the available package. **Table 5** provides a description for each pin.

Figure 10 ■ Pin Configuration (Top View-Bumps Down)

Table 5 ■ Pin Descriptions for PE29102

| Pin No.                                  | Pin<br>Name       | Descr' ,on                                                                                    |  |  |  |  |

|------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                        | HSG <sub>PD</sub> | High-side gate vive pull-d                                                                    |  |  |  |  |

| 2                                        | HSS               | High-si source                                                                                |  |  |  |  |

| 3                                        | HSB               | Hi tde bias                                                                                   |  |  |  |  |

| 4                                        | NC •              | do contaction (ground or fix                                                                  |  |  |  |  |

| 5                                        | <b>L</b> H        | Dead-time of pol resistor sets LSG falling to HSG and delay (external resistor to GND)        |  |  |  |  |

| 6                                        | HSG <sub>PI</sub> | High-side gate drive pull-up                                                                  |  |  |  |  |

| 7 <sup>(*)</sup>                         |                   | Enable vive low, tri-state outputs where gh                                                   |  |  |  |  |

| 8(*)                                     | IN                | ntrol input                                                                                   |  |  |  |  |

| 9                                        | LSG               | Low-side gate drive pull-up                                                                   |  |  |  |  |

| 10                                       | ACTL              | Controls the polarity of the gate driver outputs                                              |  |  |  |  |

| 11                                       | GND               | Ground                                                                                        |  |  |  |  |

| 12                                       | LSG <sub>PD</sub> | Low-side gate drive pull-down                                                                 |  |  |  |  |

| 13                                       | LSS               | Low-side source                                                                               |  |  |  |  |

| 14                                       | LSB               | Low-side bias                                                                                 |  |  |  |  |

| 15                                       | V <sub>DD</sub>   | +5V supply voltage                                                                            |  |  |  |  |

| 16                                       | RDHL              | Dead-time control resistor sets HSG falling to LSG rising delay (external resistor to ground) |  |  |  |  |

| Note: * Internal 100k pull down resistor |                   |                                                                                               |  |  |  |  |

DOC-81227-7 – (11/2018) Page 13 of 16

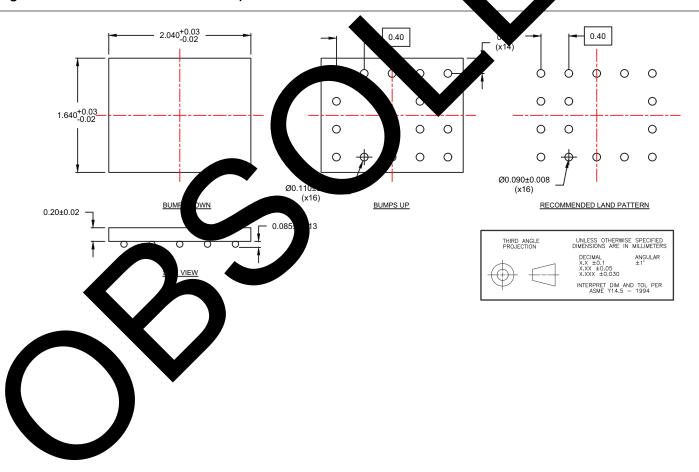

# **Die Mechanical Specifications**

This section provides the die mechanical specifications for the PE29102.

Table 6 ■ Die Mechanical Specifications for PE29102

| Parameter                  | Min | Тур         | Max | Unit | Tes condition                                                      |

|----------------------------|-----|-------------|-----|------|--------------------------------------------------------------------|

| Die size, singulated (x,y) |     | 2040 × 1640 |     | μm   | In alting sarrare,<br>ax tole ———————————————————————————————————— |

| Wafer thickness            | 180 | 200         | 220 | μm   |                                                                    |

| Wafer size                 |     |             |     | μр   |                                                                    |

| Bump pitch                 |     | 400         |     | um   |                                                                    |

| Bump height                |     | 85          |     | μm   |                                                                    |

| Bump diameter              |     | 110         |     | μm   | max tolerance = ±17                                                |

Figure 11 ■ Recommended Land Pattern for PE29102

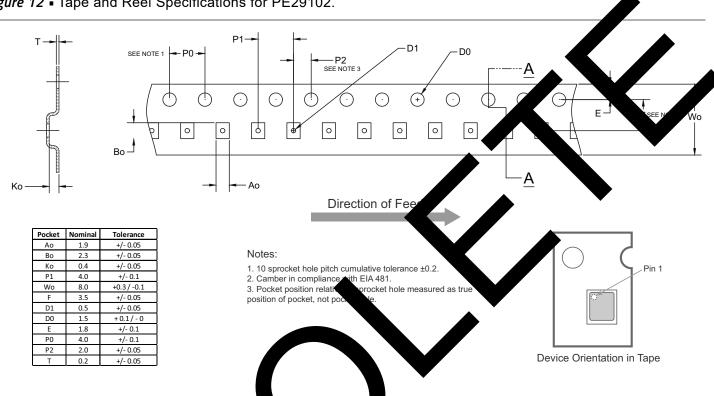

# **Tape and Reel Specification**

This section provides tape-and-reel information for the PE29102.

Figure 12 ■ Tape and Reel Specifications for PE29102.

## **Ordering Information**

Table 7 lists the available ordering code for the PE29102.

#### Table 7 ■ Order Code for PE29102

| Order Codes | Description       | Packaging            | Shir ig Methr |

|-------------|-------------------|----------------------|---------------|

| PE29102A-X  | PE29102 flip chip | Die on tape and reel | 5 vits/7      |

| PE29102A-Z  | PE29102 flip chip | Die on tape and reel | 3000 b T&R    |

### **Document Categories**

#### Advance Information

The product is in a formative or design stage. The data set contains design stage target specifications for product development. Specifications and features may change in any manner with

#### **Preliminary Specification**

The datasheet contains preliminary a. Addition of data in the be added at a later date, pSemi reserves the right to change specifications at any time without notice in order to supply the social productions are supply to the social production of the supply the supply

#### Product Specification

The datasheet contained and data in the even service des to change the specifications, pSemi will notify customers of the intended changes by issuing a CNF (Creative Notification).

#### Sales Contact

For additional information intact Sales ales@psemi.com.

#### Dis antien

The information in the cumers of leved to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's principle or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or spin life, or in any are cation in which the failure of the pSemi product could create a situation in which personal injury or death might occur. The pSemi product could be producted in the use of its products in such applications.

#### Pat. States of

pSemi products are protected under one or more of the following U.S. patents: patents.psemi.com

### Copyright and Trademark

©2018, pSemi Corporation. All rights reserved. The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.