# **Product Description**

The PE4235 RF Switch is designed to cover a broad range of applications from near DC to 4000 MHz. This single-supply reflective switch integrates on-board CMOS control logic driven by a simple, single-pin CMOS or TTL control input. Using a nominal +3-volt power supply, a 1 dB compression point of +15 dBm can be achieved. The PE4235 also exhibits outstanding isolation of better than 40 dB at 1000 MHz and is offered in a small 3x3 mm DFN package.

The PE4235 is manufactured on Peregrine's UltraCMOS™ process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate, offering the performance of GaAs with the economy and integration of conventional CMOS.

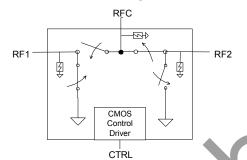

Figure 1. Functional Diagram

# **Product Specification** PE4235

### SPDT UltraCMOS™ RF Switch DC - 4000 MHz

#### **Features**

- Single 3.0-volt power supply

- Low insertion loss: 0.40 dB at 1000 MHz, 0.45 dB at 2000 MHz

- High isolation of 40 dB at 1000 MHz, 30 dB at 2000 MHz

- Typical 1 dB compression point of +15 dBm

- Single-pin CMOS or TTL logic control

- Available in a 6-lead DFN package

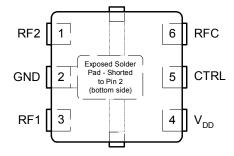

Figure 2. Package Type 6-lead DFN

Table 1. Electrical Specifications @ +25 °C,  $V_{DD}$  = 3 V (ZS = ZL = 50  $\Omega$ )

| Parameter                        | Conditions                        | Minimum  | Typical      | Maximum      | Units     |

|----------------------------------|-----------------------------------|----------|--------------|--------------|-----------|

| Operating Frequency <sup>1</sup> |                                   | DC       |              | 4000         | MHz       |

| Insertion Loss                   | 1000 MHz<br>2000 MHz              |          | 0.40<br>0.45 | 0.50<br>0.60 | dB<br>dB  |

| Isolation – RFC to RF1/RF2       | 1000 MHz<br>2000 MHz              | 39<br>29 | 40<br>30     |              | dB<br>dB  |

| Isolation – RF1 to RF2           | 1000 MHz<br>2000 MHz              | 36<br>28 | 37<br>29     |              | dB<br>dB  |

| Return Loss                      | 1000 MHz<br>2000 MHz              | 20<br>17 | 22<br>19     |              | dB<br>dB  |

| 'ON' Switching Time              | CTRL to 0.1 dB final value, 2 GHz |          | 200          |              | ns        |

| 'OFF' Switching Time             | CTRL to 25 dB isolation, 2 GHz    |          | 90           |              | ns        |

| Video Feedthrough <sup>2</sup>   |                                   |          | 2.5          |              | $mV_{pp}$ |

| Input 1 dB Compression           | 2000 MHz                          | 13.5     | 15           |              | dBm       |

| Input IP3                        | 2000 MHz, 5 dBm                   | 32.5     | 36           |              | dBm       |

Notes: 1. Device linearity will begin to degrade below 10 MHz.

<sup>2.</sup> The DC transient at the output of any port of the switch when the control voltage is switched from Low to High or High to Low in a 50  $\Omega$  test set-up, measured with 1ns risetime pulses and 500 MHz bandwidth.

Figure 3. Pin Configuration

Table 2. Pin Descriptions

| Pin<br>No. | Pin<br>Name | Description                                                                                                                                                                                                  |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RF2         | RF2 port. <sup>1</sup>                                                                                                                                                                                       |

| 2          | GND         | Ground Connection. Traces should be physically short and connected to the ground plane. This pin is connected to the exposed solder pad that also must be soldered to the ground plane for best performance. |

| 3          | RF1         | RF1 port. <sup>1</sup>                                                                                                                                                                                       |

| 4          | $V_{DD}$    | Nominal 3 V supply connection.                                                                                                                                                                               |

| 5          | CTRL        | CMOS or TTL logic level:<br>High = RFC to RF1 signal path<br>Low = RFC to RF2 signal path                                                                                                                    |

| 6          | RFC         | Common RF port for switch,1                                                                                                                                                                                  |

Notes: 1. All RF pins must be DC blocked with an external series capacitor or held at 0 V<sub>DC</sub>.

Table 3. DC Electrical Specifications

| Parameter                                                    | Min          | Тур | Max                 | Units |

|--------------------------------------------------------------|--------------|-----|---------------------|-------|

| V <sub>DD</sub> Power Supply Voltage                         | 2.7          | 3.0 | 3.3                 | V     |

| $I_{DD}$ Power Supply Current $(V_{DD} = 3V, V_{CNTL} = 3V)$ |              | 250 | 500                 | nA    |

| Control Voltage High                                         | $0.7xV_{DD}$ |     |                     | V     |

| Control Voltage Low                                          |              |     | 0.3xV <sub>DD</sub> | V     |

**Table 4. Absolute Maximum Ratings**

| Symbol            | Parameter/Conditions                     | Min  | Max                   | Units |

|-------------------|------------------------------------------|------|-----------------------|-------|

| $V_{DD}$          | Power Supply Voltage                     | -0.3 | 4.0                   | V     |

| Vı                | Voltage on any input except for CTRL pin | -0.3 | V <sub>DD</sub> + 0.3 | V     |

| $V_{\text{CTRL}}$ | Voltage on CTRL pin                      |      | 5                     | V     |

| T <sub>ST</sub>   | Storage temperature range                | -65  | 150                   | °C    |

| T <sub>OP</sub>   | Operating temperature range              | -40  | -40 85                |       |

| P <sub>IN</sub>   | Input power (50 Ω)                       |      | 19                    | dBm   |

| $V_{ESD}$         | ESD Voltage (Human Body<br>Model)        |      | 200                   | ٧     |

Absolute Maximum Ratings are those values listed in the above table. Exceeding these values may cause permanent device damage. Functional operation should be restricted to the limits in the DC Electrical Specifications table. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **Control Logic Input**

The control logic input pin (CTRL) is typically driven by a 3-volt CMOS logic level signal. For flexibility to support systems that have 5-volt control logic drivers, the control logic input has been designed to handle a standard 5-volt TTL control signal. This TTL control signal input must not exceed 5-volts or damage to the switch could result.

Table 5. Control Logic Truth Table

| Control Voltage         | Signal Path |  |

|-------------------------|-------------|--|

| CTRL = CMOS or TTL High | RFC to RF1  |  |

| CTRL = CMOS or TTL Low  | RFC to RF2  |  |

### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in Table 4.

#### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UltraCMOS™ devices are immune to latch-up.

# Typical Performance Data @ -40 °C to 85 °C (Unless Otherwise Noted)

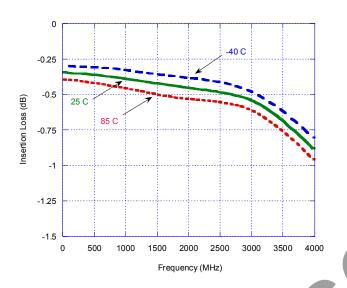

Figure 4. Insertion Loss - RFC to RF1

Figure 5. Input 1dB Compression Point and IIP3

IIP3 -40 C 40 25 C 1dB Compression Point (dBm) 30 30 IIP3 (dBm) 20 1dB Compression 10 -40 C 0 4000 1000 1500 2500 3000 3500 Frequency (MHz)

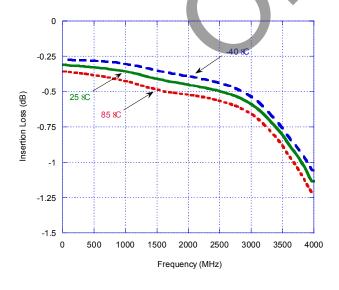

Figure 6. Insertion Loss - RFC to RF2

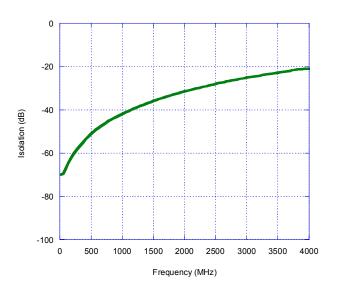

Figure 7. Isolation - RFC to RF1 T = 25 °C

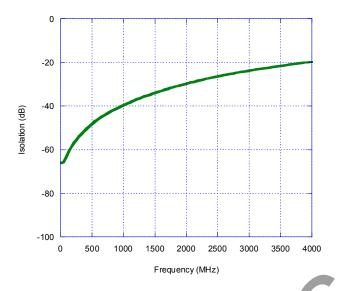

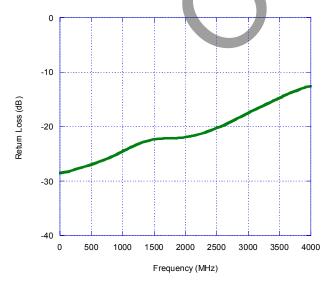

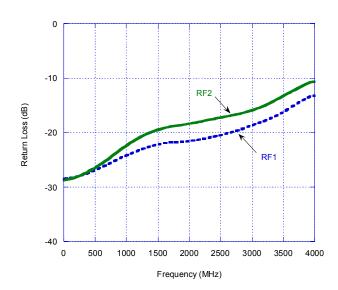

# Typical Performance Data @ 25 °C

Figure 8. Isolation – RFC to RF2

Figure 9. Isolation - RF1 to RF2, RF2 to RF1

0 -20 RF2 -40 Isolation (dB) -60 4000 500 1000 1500 2000 2500 3000 3500 Frequency (MHz)

Figure 10. Return Loss - RFC

Figure 11. Return Loss - RF1, RF2

### **Evaluation Kit**

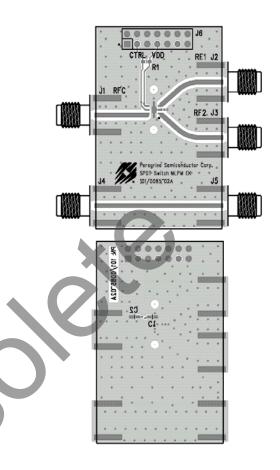

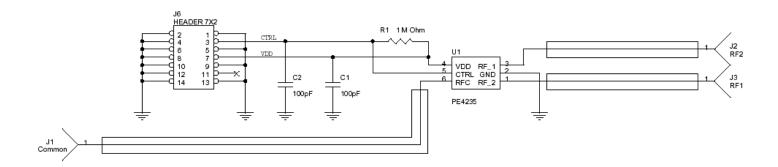

The SPDT Switch Evaluation Kit board was designed to ease customer evaluation of the PE4235 SPDT switch. The RF common port is connected through a 50  $\Omega$  transmission line to the top left SMA connector, J1. Port 1 and Port 2 are connected through 50  $\Omega$  transmission lines to the top two SMA connectors on the right side of the board, J2 and J3. A through transmission line connects SMA connectors J4 and J5. This transmission line can be used to estimate the loss of the PCB over the environmental conditions being evaluated.

The board is constructed of a two metal layer FR4 material with a total thickness of 0.031". The bottom layer provides ground for the RF transmission lines. The transmission lines were designed using a coplanar waveguide with ground plane model using a trace width of 0.0476", trace gaps of 0.030", dielectric thickness of 0.028", metal thickness of 0.0021" and  $\epsilon_{r}$  of 4.4.

J6 provides a means for controlling DC and digital inputs to the device. Starting from the lower left pin, the second pin to the right (J6-3) is connected to the device CTRL input. The fourth pin to the right (J6-7) is connected to the device V<sub>DD</sub> input. A decoupling capacitor (100 pF) is provided on both CTRL and V<sub>DD</sub> traces. It is the responsibility of the customer to determine proper supply decoupling for their design application. Removing these components from the evaluation board has not been shown to degrade RF performance.

Figure 12. Evaluation Board Layouts

Peregrine Specification 101/0085

Figure 13. Evaluation Board Schematic Peregrine Specification 102/0108

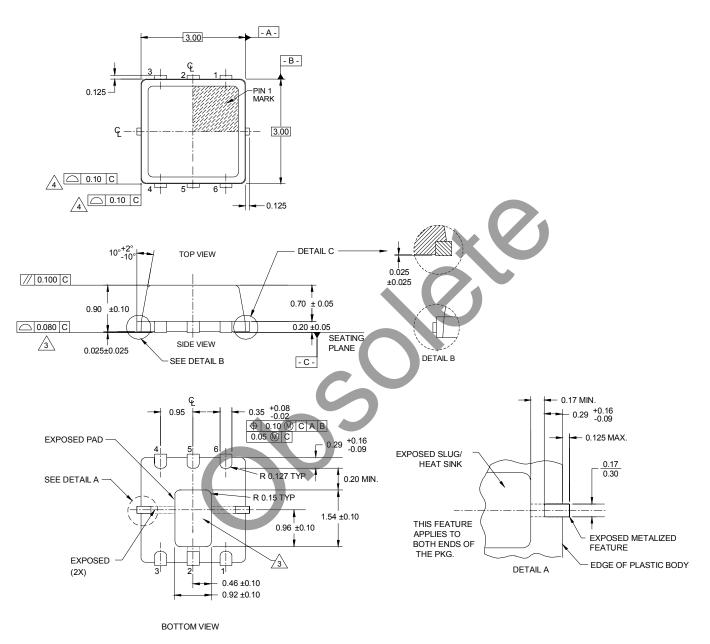

# Figure 14. Package Drawing

6-lead DFN

- 1. DIMENSIONS AND TOLERANCES ARE PER ANSI Y14.5

- 2. DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

3 COPLANARITY APPLIES TO EXPOSED HEAT SLUG AS WELL AS THE TERMINALS.

4 PROFILE TOLERANCE APPLIES TO PLASTIC BODY ONLY.

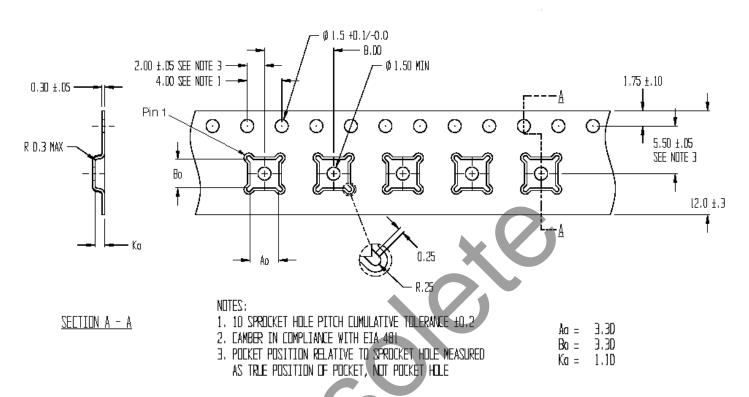

Figure 14. Tape and Reel Specifications

6-lead DFN

Table 6. Dimensions

| Dimension    | DFN 3x3 mm   |  |  |

|--------------|--------------|--|--|

| Ao           | 3.23 ± 0.1   |  |  |

| Во           | 3.17 ± 0.1   |  |  |

| Ko           | 1.37 ± 0.1   |  |  |

| Р            | 4 ± 0.1      |  |  |

| W            | 8 +0.3, -0.1 |  |  |

| Т            | 0.254 ± 0.02 |  |  |

| R7 Quantity  | 3000         |  |  |

| R13 Quantity | N.A.         |  |  |

Note: R7 = 7 inch Lock Reel, R13 = 13 inch Lock Reel

**Table 7. Ordering Information**

| Order Code | Part Marking | Description                | Package                 | Shipping Method        |

|------------|--------------|----------------------------|-------------------------|------------------------|

| 4235-01    | 4235         | PE4235-06DFN 3x3mm-12800F  | 6-lead 3x3 mm DFN       | 12800 units / Canister |

| 4235-02    | 4235         | PE4235-06DFN 3x3mm-3000C   | 6-lead 3x3 mm DFN       | 3000 units / T&R       |

| 4235-00    | PE4235-EK    | PE4235-06DFN 3x3mm-EK      | Evaluation Kit          | 1 / Box                |

| 4235-51    | 4235         | PE4235G-06DFN 3x3mm-12800F | Green 6-lead 3x3 mm DFN | 12800 units / Canister |

| 4235-52    | 4235         | PE4235G-06DFN 3x3mm-3000C  | Green 6-lead 3x3 mm DFN | 3000 units / T&R       |

### Sales Offices

#### The Americas

#### **Peregrine Semiconductor Corporation**

9450 Carroll Park Drive San Diego, CA 92121 Tel: 858-731-9400 Fax: 858-731-9499

#### Europe

### **Peregrine Semiconductor Europe**

Bâtiment Maine 13-15 rue des Quatre Vents F-92380 Garches, France Tel: +33-1-47-41-91-73 Fax: +33-1-47-41-91-73

### **Space and Defense Products**

#### Americas:

Tel: 858-731-9453 Europe, Asia Pacific: 180 Rue Jean de Guiramand

13852 Aix-En-Provence Cedex 3, France

Tel: +33(0) 4 4239 3361 Fax: +33(0) 4 4239 7227

#### North Asia Pacific

#### Peregrine Semiconductor K.K.

Teikoku Hotel Tower 10B-6 1-1-1 Uchisaiwai-cho, Chiyoda-ku Tokyo 100-0011 Japan Tel: +81-3-3502-5211

Fax: +81-3-3502-5213

#### Peregrine Semiconductor, Korea

#B-2402, Kolon Tripolis, #210 Geumgok-dong, Bundang-gu, Seongnam-si Gyeonggi-do, 463-480 S. Korea

Tel: +82-31-728-4300 Fax: +82-31-728-4305

## South Asia Pacific

#### Peregrine Semiconductor, China

Shanghai, 200040, P.R. China Tel: +86-21-5836-8276 Fax: +86-21-5836-7652

For a list of representatives in your area, please refer to our Web site at: www.psemi.com

#### Data Sheet Identification

### Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

### **Preliminary Specification**

The data sheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### Product Specification

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a DCN (Document Change Notice).

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, and UTSi are registered trademarks and UltraCMOS and HaRP are trademarks of Peregrine Semiconductor Corp.