# PE53210

Document Category: Product Specification

A Murata Company

Dual Channel Switch LNA Module, 3.3 GHz - 3.8 GHz

# Features

- Wide frequency range with internal matching

- Integrates dual-channel LNA with bypass and high power switch

- Max RF input power

- 5W Pavg for long term

- 10W Pavg for short term

- 1.65 dB noise figure

- 29 dBm OIP3/ 32 dB gain at full gain mode

- +105 °C operating temperature

- Low power consumption: 90 mA per channel

- Compact package size of 32-lead 5x5 mm

# Applications

- 4G/4.5G TD-LTE macro/micro cell

- Pre-5G/5G massive MIMO systems

- Receiver protection system

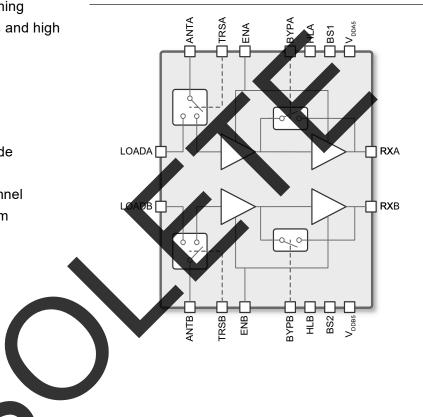

Figure 1 • PE53210 Functional Diagram

# **Product Description**

The PE53210 is a highly integrated front-end module targeted for wireless infrastructure applications such as TDD macro/micro base stations and MIMO applications. It is designed for use at the front end of a receiver chain for TDD-based systems. The PE53210 is ideally suited for 4G or next-generation 5G solutions, or small cell applications.

The dual-channel receiver integrates two independent LNAs with bypass function and a high power switch. The PE53210 can be utilized across the 3.3–3.8 GHz frequency range with internal impedance matching networks.

This receiver utilizes pSemi's UltraCMOS SOI technology which supports input RF power signal up to 5W average power, assuming 8 dB PAR and very low noise figure, excellent linearity and very low power consumption. Each channel is controlled individually within the selected frequency band, which allows more flexibility in the system design.

©2017, 2018, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

# Absolute Maximum Ratings

Exceeding absolute maximum ratings listed in **Table 1** may cause permanent damage. Operation should be restricted to the limits in **Table 2**. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

## **ESD** Precautions

When handling this UltraCMOS device, observe the same precautions as with any other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in **Table 1**.

Table 1 • Absolute Maximum Ratings for PE53210

| Parameter                                                                                                                                                        | Rating     | Unit      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| Power supply voltage                                                                                                                                             | 5.50       | V         |

| Control input voltage                                                                                                                                            | 3.60       | V         |

| Storage temperature range                                                                                                                                        | -65 to 150 | °C        |

| RF input power, single event, average <sup>(1)</sup>                                                                                                             | 40         | dBm       |

| LNA input power                                                                                                                                                  | 22         | dBm       |

| Human-body model, all pins <sup>(2)</sup>                                                                                                                        | 1000       | V         |

| Charged device model, all pins <sup>(3)</sup>                                                                                                                    | 500        |           |

| <ol> <li>TX mode, 10 min duration, 105 °C, 8 dB PAR</li> <li>Human body model (MIL-STD 883 Method 30</li> <li>Charged device model (JEDEC JESD22-210)</li> </ol> | )15)       | switching |

# **Recommended Operating Conditions**

**Table 2** lists the recommending operating conditions for the PE53210. Devices should not be operated outside the recommended operating conditions listed below.

#### Table 2 • Recommended Operating Conditions for PE53210

| Parameter                               | Min   | Тур | Мах  | Unit |

|-----------------------------------------|-------|-----|------|------|

| V <sub>DD</sub> positive supply voltage | 4.75  |     | 5.25 | V    |

| Control voltage high                    | 1.17  |     | 3.60 | V    |

| Control voltage low                     | -0.30 |     | 0.60 | V    |

| Digital input leakage current           | -20   | 0   | 20   | μA   |

| Operating temperature range             | -40   | 25  | 105  | °C   |

# **Electrical Specifications**

**Table 3** provides the PE53210 key electrical specifications @ +25 °C,  $V_{DD}$  = 5V (Z<sub>S</sub> = Z<sub>L</sub> = 50 $\Omega$ ), unless otherwise specified.

#### Table 3 • PE53210 Electrical Specifications

| Parameter                    | Condition                                                                                                                                                                  | Min              | Тур              | Мах                  | Unit |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------|------|

| Frequency range              |                                                                                                                                                                            | 3300             |                  | 3800                 | MHz  |

| Input return loss            | ANTA or ANTB, Rx mode<br>at 3300 MHz<br>at 3500 MHz<br>at 3800 MHz                                                                                                         |                  | 13.5<br>20<br>10 |                      | dB   |

| Output return loss           | At RXA or RXB, Rx mode<br>at 3300 MHz<br>at 3500 MHz<br>at 3800 MHz                                                                                                        |                  | 7<br>8.5<br>8    |                      | dB   |

| Insertion loss               | Tx operation mode, ANT-Load                                                                                                                                                |                  | 0.7              |                      | dB   |

| RF max input power<br>(Pavg) | Average value; No damage for long time operation; RE Load connected to load with -10dB return loss.<br>LTE Signal PAR 8dB                                                  | 5                |                  |                      | W    |

| TX/RX switching time         | RX to TX or TX to RX, 50% cntl to 10/90 RF                                                                                                                                 |                  | 550              |                      | ns   |

| Bypass switching time        | Bypass enable or disable, 50% cntl to 10/90 RF                                                                                                                             |                  | 220              |                      | ns   |

| Switch isolation             | RX mode ANT to load termination                                                                                                                                            |                  | 20               |                      | dB   |

| Switch isolation             | TX mode, LNA off, ANT to RX OUT                                                                                                                                            |                  | 60               |                      | dB   |

| Channel isolation            | RX mode, RX to RX                                                                                                                                                          |                  | 38               |                      | dB   |

| Channel isolation            | TX mode, TX to TX                                                                                                                                                          |                  | 46               |                      | dB   |

| Cross isolation              | RX mode, ANT1 to RX2                                                                                                                                                       |                  | 73               |                      | dB   |

| Cross isolation              | RX mode, LNA 2 bypass, ANT1 to RX2                                                                                                                                         |                  | 60               |                      | dB   |

| In-band spurious<br>emission | Rx mode at Rx out with pip = .49 dBm<br>Pin is a CW signal swept across frequency range. Spec refers to any<br>spurious mixing product that occurs across frequency range. |                  | -85              |                      | dBc  |

| Out-of-band emission         | Rx mode at Rx out/from DC to 12275 MHz<br>Measure Pout with IBW = 4.5 MHz over frequency range with no input<br>power applied.                                             |                  | -65              |                      | dBm  |

| Full Gain Mode               |                                                                                                                                                                            |                  |                  |                      | •    |

| Supply current               | 5V supply, per channel, at max gain                                                                                                                                        |                  | 90               |                      | mA   |

| Bypass mode supply current   | 5V supply, per channel, second amp bypassed                                                                                                                                |                  | 25               |                      | mA   |

| Gain                         | Full gain mode<br>at 3300 MHz<br>at 3500 MHz<br>at 3800 MHz                                                                                                                | 31<br>29<br>26.5 | 32<br>30.5<br>28 | 33.6<br>31.9<br>29.8 | dB   |

| Gain flatness                | Full gain mode                                                                                                                                                             |                  | 0.8              |                      | dB   |

| Bypass gain                  | Bypass mode                                                                                                                                                                | 11.7             | 14               |                      | dB   |

| Bypass gain flatness         | Full gain mode                                                                                                                                                             | 1                | 0.6              |                      | dB   |

## PE53210 Dual Channel Switch LNA Module

### Table 3 • PE53210 Electrical Specifications (Cont.)

| OIP3 <sup>(1)</sup> FullBypass OIP3 <sup>(2)</sup> BypOP1dBFullBypass OP1dBBypLow Power ModeSVLow power mode currentSVBypass mode supply<br>currentSV | gain or bypass mode<br>gain mode<br>ass mode<br>gain mode<br>ass mode<br>supply, per channel<br>supply, per channel, second amp bypassed | 28<br>22 | 1.65<br>29<br>24<br>19<br>13 | 1.9  | dB<br>dBm<br>dBm<br>dBm<br>dBm |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------|------|--------------------------------|

| Bypass OIP3 <sup>(2)</sup> Byp<br>OP1dB Full<br>Bypass OP1dB Byp<br>Low Power Mode<br>Low power mode current 5V<br>Bypass mode supply<br>current 5V   | ass mode<br>gain mode<br>ass mode<br>supply, per channel                                                                                 |          | 24<br>19                     |      | dBm<br>dBm                     |

| OP1dBFullBypass OP1dBBypLow Power ModeEventLow power mode current5VBypass mode supply<br>current5V                                                    | gain mode<br>ass mode<br>supply, per channel                                                                                             | 22       | 19                           |      | dBm                            |

| Bypass OP1dB     Byp       Low Power Mode     5V       Low power mode current     5V       Bypass mode supply current     5V                          | ass mode<br>supply, per channel                                                                                                          |          |                              |      |                                |

| Low Power Mode           Low power mode current         5V           Bypass mode supply<br>current         5V                                         | supply, per channel                                                                                                                      |          | 13                           |      | dBm                            |

| Low power mode current5VBypass mode supply<br>current5V                                                                                               |                                                                                                                                          |          |                              |      | uDIII                          |

| Bypass mode supply current 5V                                                                                                                         |                                                                                                                                          |          |                              |      |                                |

| current                                                                                                                                               | aunaly per channel accord ama hypercod                                                                                                   |          | 75                           |      | mA                             |

| Gain Full                                                                                                                                             | supply, per channel, second amp bypassed                                                                                                 | X        | 25                           |      | mA                             |

| -                                                                                                                                                     | gain mode                                                                                                                                | 26.5     | 28                           |      | dB                             |

| Gain flatness Any                                                                                                                                     | 100 MHz bandwidth, at full gain                                                                                                          |          | 0.75                         |      | dB                             |

| Bypass gain Byp                                                                                                                                       | ass mode                                                                                                                                 | 12       | 14                           |      | dB                             |

| Bypass gain flatness Any                                                                                                                              | 100 MHz bandwidth, second amp bypassed                                                                                                   |          | 0.75                         |      | dB                             |

| NF Full                                                                                                                                               | gain or bypass mode                                                                                                                      |          | 1.65                         | 1.90 | dB                             |

| OIP3 <sup>(1)</sup> Full                                                                                                                              | gain mode                                                                                                                                | 26       | 27.5                         |      | dBm                            |

| Bypass OIP3 <sup>(2)</sup> Byp                                                                                                                        | ass mode                                                                                                                                 | 21.5     | 23.5                         |      | dBm                            |

| OP1dB Max                                                                                                                                             | gain mode                                                                                                                                |          | 19                           |      | dBm                            |

| Bypass OP1dB Byp                                                                                                                                      | ass mode                                                                                                                                 |          | 13                           |      | dBm                            |

| 1) -35 dBm input power, 1 MHz<br>2) -25 dBm input power, 1 MHz                                                                                        |                                                                                                                                          |          |                              |      |                                |

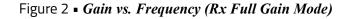

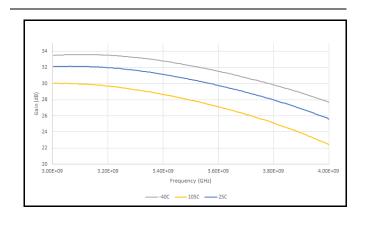

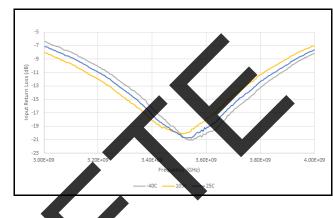

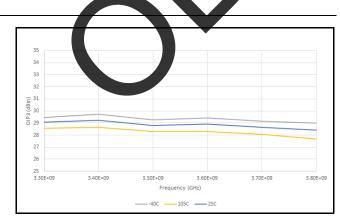

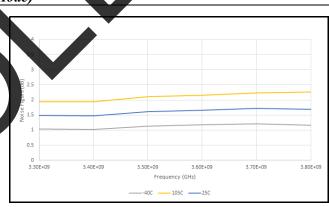

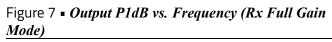

# **Typical Performance Data**

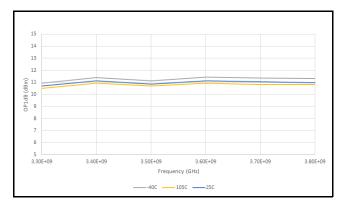

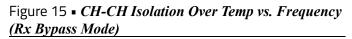

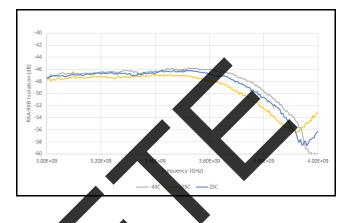

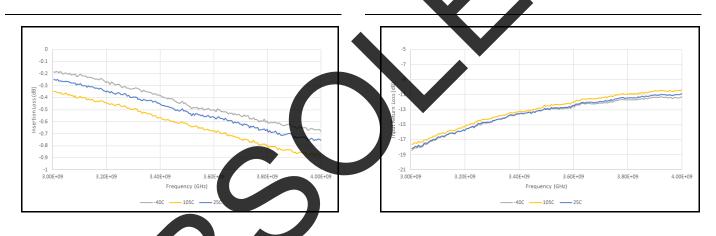

Figure 2 through Figure 18 show the typical performance data at nominal condition, unless otherwise specified.

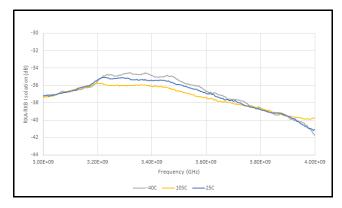

Figure 3 • ANT Return Loss vs. Frequency (Rx Full Gain Mode)

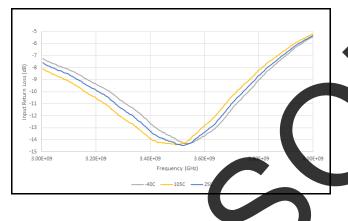

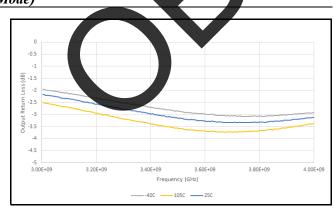

Figure 4 • *Rx Out Return Loss vs. Frequency (Rx Full Gain Mode)*

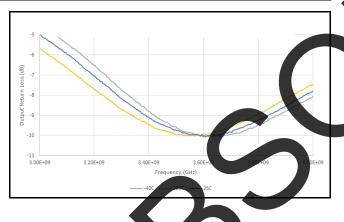

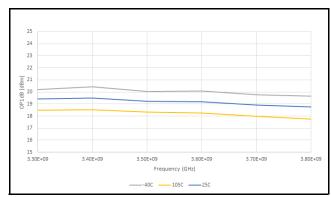

Figure 6 • OIP3 vs. Frequency (Rx Full Gain Mode)

Figure 8 • CH-CH Isolation vs. Frequency (Rx Full Gain Mode)

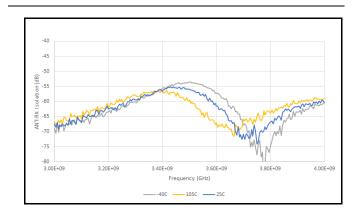

Figure 10 • ANT Return Loss Over Temp vs. Frequency (Rx Bypass Mode)

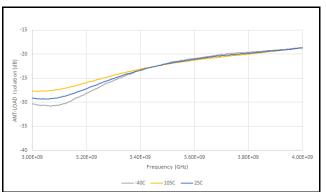

Figure 12 • Noise Figure Over Temp vs. Frequency (Rx Bypass Mode)

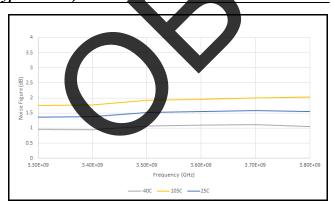

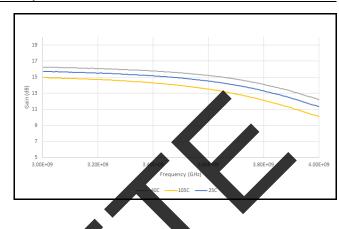

Figure 9 • *Gain Over Temp vs. Frequency (Rx Bypass Mode)*

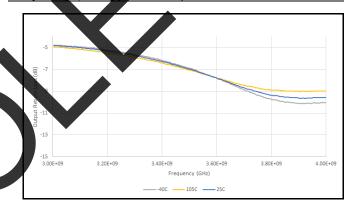

Figure 11 • Rx Out Return Loss Over Temp vs. Frequency (Rx Bypgss Mode)

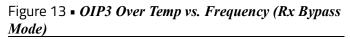

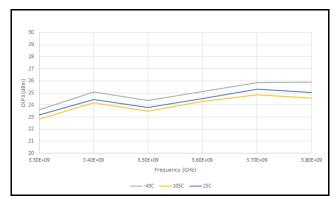

Figure 14 • Output P1dB Over Temp vs. Frequency (Rx Bypass Mode)

Figure 16 • Insertion Loss vs. Frequency (Tx Mode)

Figure TANT Beturn Loss vs. Frequency (Tx Mode)

Figure 18 • *Rx Out Return Loss vs. Frequency (Tx Mode)*

Figure 19 • ANT-Rx Isolation vs. Frequency (Tx Mode)

## PE53210 Dual Channel Switch LNA Module

# Figure 20 • ANT-Load Isolation vs. Frequency (Rx Mode)

120 KΩ (R9, R10)

200 KΩ (R9, R10)

120 KΩ (R9)

200 KΩ (R9)

**Resistor Value**

# Supply Current vs. Resistor Value

Table 4 • Supply Current vs. Resistor Value

Part Number

PE53210/PE53211

PE53110/PE53111

|   | Γ                        |          |                 |              |                |                      |                 |          |

|---|--------------------------|----------|-----------------|--------------|----------------|----------------------|-----------------|----------|

|   |                          | -40      |                 |              |                |                      |                 |          |

|   |                          | -41      |                 |              |                |                      |                 |          |

|   |                          | -42      |                 |              |                |                      |                 |          |

|   |                          | 9 -43    |                 |              |                |                      |                 |          |

|   |                          | § -44    |                 |              |                |                      |                 |          |

|   | 100                      | -45      |                 |              |                |                      |                 |          |

|   | 2                        | -46      |                 |              |                | -                    |                 |          |

|   | dah) melan lant avr. Avr | -47      |                 |              | and the second |                      | MOCHAN CANANA C |          |

|   |                          | -48      | -               | march of the | Alana .        |                      |                 |          |

|   |                          | -49      |                 |              |                |                      |                 |          |

|   |                          | -50      |                 |              |                |                      |                 |          |

|   |                          | 3.00E+09 | 3.20            | E+09         | 3.40E+09       | 3.602+09             | 3.80E+09        | 4.00E+09 |

|   |                          |          |                 |              |                | ncy (GHz)<br>105C25C |                 |          |

|   |                          |          |                 |              |                |                      | $\checkmark$    |          |

| ] |                          |          |                 |              |                |                      |                 |          |

|   |                          |          |                 |              |                |                      |                 |          |

| J |                          |          |                 |              |                |                      |                 |          |

|   |                          |          |                 |              |                |                      |                 |          |

|   |                          |          |                 |              |                |                      |                 |          |

|   |                          |          |                 |              |                |                      |                 |          |

|   |                          |          |                 |              |                |                      |                 |          |

| ] |                          |          |                 |              |                | 1050250              |                 |          |

|   |                          |          |                 |              |                | 1050250              | pply Curr       | rent—    |

|   |                          | Sup      | ply C<br>full G |              | tec<br>1t—     | 105C -25C            | pply Curr       |          |

90 mA

75 mA

90 mA

75 mA

Figure 21 • CH-CH Isolation vs. Frequency (Tx Mode)

25 mA

25 mA

25 mA

25 mA

\_

## PE53210 **Dual Channel Switch LNA Module**

# **Pin Configuration**

This section provides pin information for the PE this pin

#### Fig

Table 5 • Pin Descriptions for PE53210

| his section provides pin information for the<br>PE53210. Figure 22 shows the pin configuration of<br>his device. Table 5 provides a description for each | Pin No.        | Pin<br>Name       | Description                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bin.                                                                                                                                                     | 1              | LOADA             | Channel A load                                                                                                                                                                                             |

| igure 22 • Pin Configuration (Top View)                                                                                                                  | 2–7, 18–23, 31 | GND               | Ground                                                                                                                                                                                                     |

|                                                                                                                                                          | 8              | LOADB             | Channel B load                                                                                                                                                                                             |

|                                                                                                                                                          | 9              | ANTB              | Channel B antenna                                                                                                                                                                                          |

| Pin 1 Dot<br>Marking<br>LOADA                                                                                                                            | 10             | NC                | Not connected. Pin 10 (NC)<br>must be left NOT CON-<br>NECTED at the application<br>board for proper operation.                                                                                            |

| GND         [2]         (23)         GND           GND         [3]         (22)         GND                                                              | 11             | TRSB              | Channel B high power switch                                                                                                                                                                                |

| GND (4) Exposed (2) GND                                                                                                                                  | 12             | ENB               | Channel B LNA enable                                                                                                                                                                                       |

| GND 5 Ground Pad                                                                                                                                         | 13             | BYPB              | Channel B LNA bypass control                                                                                                                                                                               |

| GND [6)<br>GND [7]<br>LOADB [8]<br>6] (2) (2) (2) (2) (2) (2) (2) (2)                                                                                    | 14             | HLB               | Channel B bias. HLB requires<br>a 120k Ohm resistor to the<br>application board GND to set<br>90 mA in Rx Full Gain mode,<br>BYPA=0.                                                                       |

| ANTB<br>NC<br>TRSB<br>BYPB<br>HLB<br>BS2<br>VDB5                                                                                                         | 15             | BS2               | Isolation. BS2 can be left NOT<br>CONNECTED for internally-<br>tied logic high. If BS2 is con-<br>nected to the TRSB control<br>pin, it will improve ANTB to<br>RXB isolation in TX mode for<br>channel B. |

|                                                                                                                                                          | 16             | V <sub>DDB5</sub> | Supply voltage                                                                                                                                                                                             |

|                                                                                                                                                          | 17             | RXB               | Channel B RF output port<br>External 39pF DC blocking<br>capacitor is required.                                                                                                                            |

|                                                                                                                                                          | 24             | RXA               | Channel A RF output port<br>External 39pF DC blocking<br>capacitor is required.                                                                                                                            |

|                                                                                                                                                          | 25             | V <sub>DDA5</sub> | Supply voltage                                                                                                                                                                                             |

|                                                                                                                                                          | 26             | BS1               | Isolation. BS1 can be left NOT<br>CONNECTED for internally-<br>tied logic high. If BS1 is con-<br>nected to the TRSA control<br>pin, it will improve ANTA to<br>RXA isolation in TX mode for<br>channel A. |

#### Table 5 • Pin Descriptions for PE53210 (Cont.)

| Pin No. | Pin<br>Name | Description                                                                                                                          |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 27      | HLA         | Channel A bias. HLA requires<br>a 120k Ohm resistor to the<br>application board GND to set<br>90 mA in Rx Full Gain mode,<br>BYPA=0. |

| 28      | BYPA        | Channel A LNA bypass control                                                                                                         |

| 29      | ENA         | Channel A LNA enable                                                                                                                 |

| 30      | TRSA        | Channel A high power switch control                                                                                                  |

| 32      | ANTA        | Channel A antenna                                                                                                                    |

| PAD     | GND         | Exposed pad: ground for<br>proper operation                                                                                          |

## **Truth Table**

Table 6 • Receiver Module Dual Channel Tx-Rx Control Logic Truth Table

| Mode              | BS1 | BS2 |   | ENB | <b>IRSA</b> | TRSB | BYPA | BYPB |

|-------------------|-----|-----|---|-----|-------------|------|------|------|

| Receive—Full Gain | 1   | 1   | 1 | 1   | 1           | 1    | 0    | 0    |

| Receive—Bypass    | 1   |     | 1 | 1   | 1           | 1    | 1    | 1    |

| Transmit          | 1   | 1   | 0 | 0   | 0           | 0    | 0    | 0    |

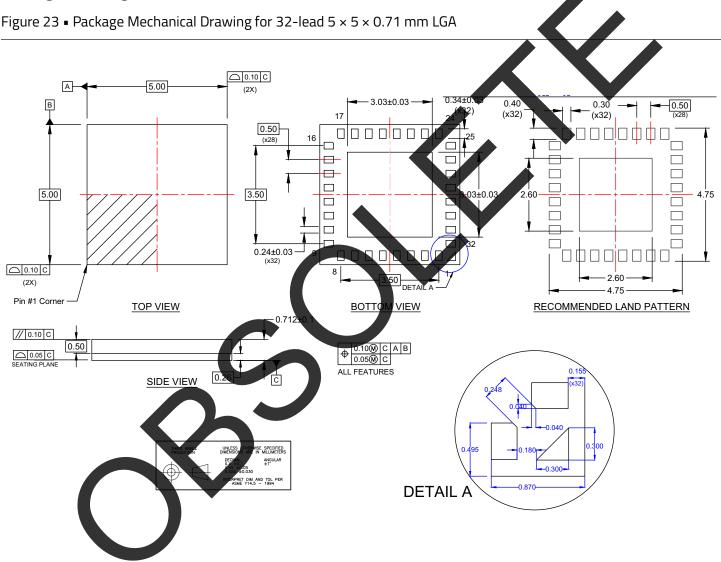

# **Packaging Information**

This section provides packaging data including the moisture sensitivity level, package drawing, package marking and tape-and-reel information.

### **Moisture Sensitivity Level**

The moisture sensitivity level rating for the PE53210 in the 32-lead 5 × 5 × 0.71 mm LGA package is MSL 3.

## **Package Drawing**

# Top-Marking Specification

Figure 24 • Package Marking Specifications for PE53210

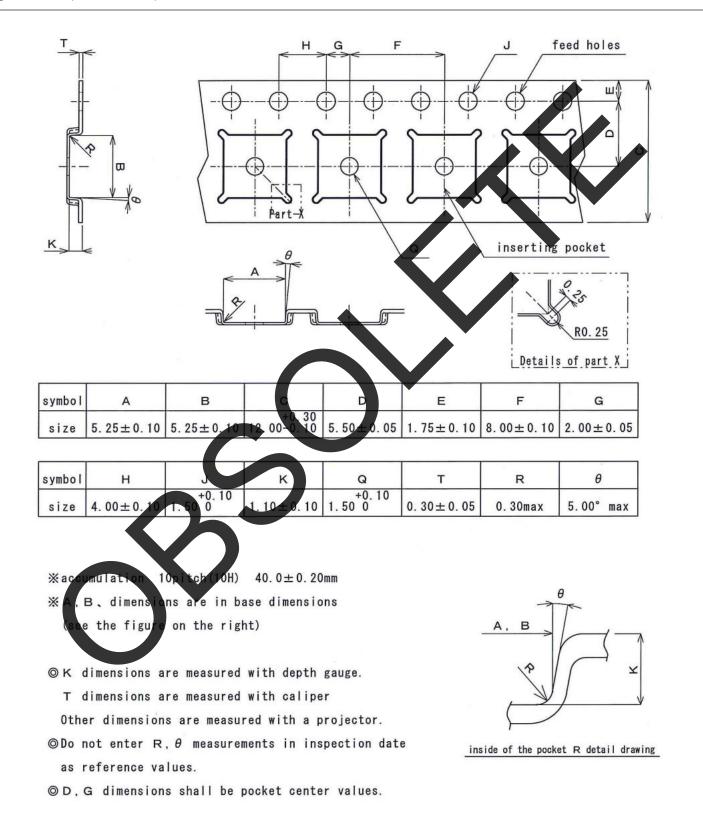

# Tape and Reel Specification

Figure 25 • Tape and Reel Specification for PE53210

## **Ordering Information**

Table 7 lists the available ordering codes for the PE53210 as well as available shipping methods.

#### Table 7 • Order Codes for PE53210

| Order Codes | Description            | Packaging          | Shipping Method |

|-------------|------------------------|--------------------|-----------------|

| PE53210A-Z  | PE53210 Switch and LNA | 32-lead 5x5 mm LGA | 3000 units/T&R  |

| EK53210-01  | PE53210 Evaluation kit | Evaluation kit     | 1/Box           |

## **Document Categories**

#### Advance Information

The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

#### **Preliminary Specification**

The datasheet contains preliminary data. Additional data may be added at a later date. pSemi reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### Product Specification

The datasheet contains final data, to the event pSemi decides to change the specifications, pSemi will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

#### Sales Conta

For additional information, contact Sales at sales@psemi.com.

#### Disclaimer

The information in this document is believed to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely at the user's own risk no patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the pSemi product could create a situation in which personal injury or death might occur. pSemi assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### Patent Statement

pSemi products are protected under one or more of the following U.S. patents: patents.psemi.com

#### Copyright and Trademark

©2017, 2018, pSemi Corporation. All rights reserved. The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.